AN INFORMAL PUBLICATION FROM ACADEMIA'S PREMIERE STORAGE SYSTEMS RESEARCH CENTER DEVOTED TO ADVANCING THE STATE OF THE ART IN STORAGE AND INFORMATION INFRASTRUCTURES.

## CONTENTS

| Parity Models I           |

|---------------------------|

| Director's Letter2        |

| Year in Review4           |

| Recent Publications5      |

| PDL News & Awards8        |

| Data Lakes 12             |

| Custom Storage Backends13 |

| Defenses & Proposals 16   |

## PDL CONSORTIUM MEMBERS

Alibaba Group Amazon Datrium Facebook Google Hewlett Packard Enterprise Hitachi, Ltd. **IBM** Research Intel Corporation Microsoft Research NetApp, Inc. Oracle Corporation Pure Storage Salesforce Samsung Semiconductor, Inc. Seagate Technology Two Sigma Western Digital

## Parity Models: Erasure-Coded Resilience for Prediction Serving Systems

Jack Kosaian, Rashmi Vinayak

Erasure codes have been widely deployed in storage and communication systems to impart resource-efficient resilience against data unavailability. In this work, we describe a new opportunity for using ideas from erasure codes: to reduce tail latency in systems that perform machine learning inference. This raises a number of new challenges compared to traditional uses of erasure codes; most notably, in this new setting, encoded data is computed over. In this work, we show that leveraging machine learning offers the promise of overcoming these challenges to enable the use of erasure codes to reduce tail latency in systems that perform machine learning inference.

Machine learning is widely deployed in production services and user-facing applications. This has increased the importance of inference, the process of returning a prediction from a trained machine learning model. Prediction-serving systems are platforms that host models for inference and deliver predictions for input queries.

To meet the demands of user-facing production services, prediction-serving systems must deliver predictions with low latency (e.g., within tens of milliseconds). Similar to other latency-sensitive services, prediction services must adhere to strict service-level objectives (SLOs). Queries that are not completed by their SLO are often useless to applications. In order to reduce SLO violations, prediction-serving systems must minimize tail latency.

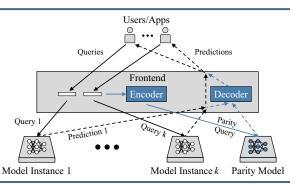

Prediction-serving systems often employ distributed architectures to support high query rates. These systems consist of a frontend, which receives queries and dispatches them to one or more model instances. Model instances perform inference and return predictions. This distributed setup is typically run in largescale, multi-tenant clusters (e.g., public clouds), where tail latency inflation is a common problem. There are numerous causes of inflated tail latencies in these settings, such as multi-tenancy and resource contention, hardware unreliability and failures, and other complex runtime interactions.

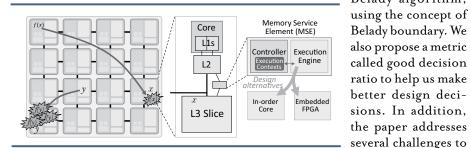

Architecture of a prediction serving system along with components introduced by ParM (shown in blue).

Due to the many causes of tail latency inflation, it is important for mitigations to be agnostic to the cause of slowdown. However, current agnostic approaches for mitigating tail latency inflation either require significant resource overhead by replicating queries, or sacrifice latency by waiting to detect a slowdown or failure before retrying.

#### FROM THE DIRECTOR'S CHAIR

## GREG GANGER

What a time we're living through. Each year, I use this space to comment on the prior year's research and personal successes of PDL's great students, staff, and faculty. And I will, after this initial paragraph. But, current events have ob-

viously had a huge impact on us all. It's difficult for me not to go on extensively about these issues, but I will restrain to this: we miss working together in our collaborations, we miss hosting and interacting in-person with our sponsors, we feel deeply for all who have suffered losses in their families and their livelihoods, and we remain dedicated to making PDL, CMU, and the world a place of equality, acceptance, and community. To all: be well, stay safe, and love thy neighbor!

Now, to the traditional function of this space: overviewing PDL's past year. It's always a pleasure to extol the successes of PDL's great people, and this year is no different. Some highlights include exciting new projects and collaborations with sponsors, continued growth and success for PDL's storage systems and cloud classes, and lots of great new activities and results in long-standing areas of strength like database systems, ML systems, and data processing infrastructure. Along the way, many students have graduated and joined PDL Consortium companies, PDL researchers have won some big awards, and many cool papers have been published. Specifics can be found throughout the newsletter, but let me highlight a few things.

Storage has been a PDL focus since its founding in the early 90s, and PDLers are exploring a number of new opportunities created by new storage technologies, new storage interfaces, and our connections to PDL Consortium companies. For example, building on our recent case study (see article) of Ceph evolution, we are exploring distributed storage back-ends specialized for zoned storage devices (e.g., ZNS SSDs or ZBR HDDs)... and we thank Western Digital for working with us to conduct real experiments. We are exploring new NVM-aware algorithms (including a recent Best Paper award) and NVM-specialized distributed redundancy approaches... and we thank Intel for enabling us to conduct real experiments. We are exploring approaches, together with Facebook, and mechanical disk failure rates over time, with the help of NetApp and Google. The new insights and ideas arising from the ability to experiment with real devices, workload traces, and failure logs are exciting to see.

PDL has also long concerned itself with resource scheduling for data processing activities, and there are exciting new activities here as well, arising to address new computing models. For example, we have been working with Microsoft to study inter-job dependencies in data lakes and their impact on resource management. By analyzing provenance data and job logs from Cosmos, Microsoft's huge data lake infrastructure, we have been identifying significant challenges currently addressed in ad hoc ways and great opportunities for maximizing the value realized from a data analytics infrastructure (see article). Research on another front has devised new approaches for handling DNN training jobs in a shared cluster. By co-adaptively deciding per-job parameters (e.g., batch size) and how many nodes to use for each job, the aggregate performance of training jobs on the cluster can be improved significantly.

We continue to work on the challenges of high-performance and large-scale storage. Exciting new results have been achieved in our work on in-situ index creation for new data, including an R&DIOO award for the DeltaFS work done jointly with LANL researchers. And, some surprising/cool applications for it

### THE PDL PACKET

#### THE PARALLEL DATA LABORATORY

School of Computer Science Department of ECE Carnegie Mellon University 5000 Forbes Avenue Pittsburgh, PA 15213-3891 voice 412•268•6716 FAX 412•268•3010

#### PUBLISHER

Greg Ganger

#### EDITOR

Joan Digney

The PDL Packet is published once per year to update members of the PDL Consortium. A pdf version resides in the Publications section of the PDL Web pages and may be freely distributed. Contributions are welcome.

#### THE PDL LOGO

Skibo Castle and the lands that comprise its estate are located in the Kyle of Sutherland in the northeastern part of Scotland. Both 'Skibo' and 'Sutherland' are names whose roots are from Old Norse, the language spoken by the Vikings who began washing ashore regularly in the late ninth century. The word 'Skibo' fascinates etymologists, who are unable to agree on its original meaning. All agree that 'bo' is the Old Norse for 'land' or 'place,' but they argue whether 'ski' means 'ships' or 'peace' or 'fairy hill.'

Although the earliest version of Skibo seems to be lost in the mists of time, it was most likely some kind of fortified building erected by the Norsemen. The present-day castle was built by a bishop of the Roman Catholic Church. Andrew Carnegie, after making his fortune, bought it in 1898 to serve as his summer home. In 1980, his daughter, Margaret, donated Skibo to a trust that later sold the estate. It is presently being run as a luxury hotel.

#### PARALLEL DATA LABORATORY

#### FACULTY

Greg Ganger (PDL Director) 412•268•1297 ganger@ece.cmu.edu

George Amvrosiadis David Andersen Nathan Beckmann Chuck Cranor Lorrie Cranor Christos Faloutsos Saugata Ghose Phil Gibbons Garth Gibson cmu.edu Mor Harchol-Balter Gauri Joshi Todd Mowry David O'Hallaron Andy Pavlo Majd Sakr M. Satyanarayanan Rashmi Vinayak

#### STAFF MEMBERS

Bill Courtright, 412•268•5485 (PDL Executive Director) wcourtright@cmu.edu Karen Lindenfelser, 412•268•6716 (PDL Administrative Manager) karen@ece.cmu.edu Jason Boles Joan Digney Chad Dougherty Mitch Franzos

#### GRADUATE STUDENTS

Abutalib Aghayev Daiyaan Arfeen Mohammad Bakhshalipour Nirav Atre Ben Berg Vilas Bhat Amirali Boroumand Sol Boucher Matt Butrovich Mengxin Cao Dominic Chen Zhiran Chen Yae Jee Cho Andrew Chung Ziqi Dong Pratik Fegade Zigiang Feng Graham Gobieski Zijing Gu Samarth Gupta lin Han Travis Hance Ankush Jain Angela Jiang Ellango Jothimurugesan Saurabh Arun Kadekodi Daehyeok Kim Thomas Kim Arvind Sai Krishnan Jack Kosaian Joseph Koshakow

Anuva Kulkarni Tian Li Wan Shen Lim Kaige Liu Elliot Lockerman Lin Ma Ankur Mallick Francisco Maturana Sara McAllister Charles McGuffey Prashanth Menon Hojin Park Aurick Qiao Brian Schwedock Damla Senol Baljit Singh Vikramraj Sitpal Suhas J Subramanya Minh Truong Dana Van Aken Jianyu Wang Zigi Wang Daniel Wong Tong Xiao Ricky Xu Dongsheng Yang Jason Yang Zhengzhe Yang Ling Zhang Qing Zheng

Giulio Zhou

Michael Kuchnik

#### UNDERGRADUATE STUDENTS

Jordi Gonzalez Julian Tutuncu-Macias

## FROM THE DIRECTOR'S CHAIR

have been found (ask George, since I don't want to steal the story). Our HeART project continues, exploring how cluster storage redundancy can and should be adaptively specialized to the diverse observed failure rates of heterogeneous HDDs. Our new Pacemaker design regulates HeART activity to allow safe, efficient adaptive redundancy that can reduce by 20% of more the disks needed in IOOK+ storage clusters... based on analyses of clusters at Google and Backblaze. There is also an exciting new project that explores how storage systems can be specialized for ML training workloads.

We are applying ML to data systems in many areas. Of course, Andy's effort to create self-driving database systems continues, with new active learning approaches, new auto-config approaches, and an emerging new database system. (He has over 20 students working on it!) We are also exploring ML-based admission policies for Flash caches, ML-based approaches for predicting when device failure rates will rise, and automated cloud storage provisioning given the huge set of available options.

Although I mentioned some examples above, there are other "systems for ML" projects ongoing. One of the coolest is the application of coded computation to ML inference to provide resilience to server failures (see front-page article). An emerging area of exploration focuses on simplifying MLops by exploiting provenance data and automating workflow exploration. Watch for cool results from this direction.

Many other ongoing PDL projects are also producing cool results... too many for me to cover. But, this newsletter and the PDL website offer more details and additional research highlights. Given the inability for us to gather in person, we did our first ever virtual PDL "Visit" Day. Attendance was strong (over 127 from our sponsor companies, compared to 35 at 2019's in-person PDL Visit Day), and we thank the many of you who participated. Based on the experience, we are planning to try some different ways of interacting with you remotely (stay tuned!), while looking forward to being able to celebrate an in-person PDL Retreat with you when circumstances permit!

I'm always overwhelmed by the accomplishments of the PDL students and staff, and it's a pleasure to work with them. As always, their accomplishments point at great things to come.

2019 PDL Workshop and Retreat.

### July 2020

- Aurick Qiao gave his speaking skills talk on "Pollux: Co-adaptive Cluster Scheduling for Goodput-Optimized Deep Learning."

- Andrew Chung presented his speaking skills talk on "Wing: Unearthing Inter-job Dependencies for Better Cluster Scheduling."

#### June 2020

- 22nd Annual/Ist Virtual PDL Spring Visit Day.

- David O'Hallaron, Professor of ECE and CS awarded the Philip L. Dowd fellowship.

- Prashanth Menon delivered his thesis proposal "On Building Robustness into Compilation-Based Main-Memory Database Query Engines."

- Dana Van Aken delivered her thesis proposal "On Automatic Database Management System Tuning Using Machine Learning."

- Huanchen Zhang presented "Order-Preserving Key Compression for In-Memory Search Trees" at SIGMOD'20. Conglong Li presented "Improving Approximate Nearest Neighbor Search through Learned Adaptive Early Termination" and Lin Ma presented "Active Learning for ML Enhanced Database Systems" at the same conference.

- Ankur Mallick and co-authors received the best paper award at

Chuck Cranor, Qing Zheng and Ankush Jain enjoying the poster session at the 2019 PDL Retreat.

ACM SIGMETRICS 2020, for

their paper on "Rateless Codes for Near-Perfect Load Balancing in Distributed Matrix-Vector Multiplication."

Mor Harchol-Balter's team presented "Simple Near-Optimal Scheduling for the M/G/I" at SIGMETRICS.

#### May 2020

- Rajat Kateja presented "TVARAK: Software-Managed Hardware Offload for Redundancy in Direct-Access NVM Storage" at the 47th Int'l Symposium on Computer Architecture.

- Phil Gibbons was a recipient of the 2019 Paris Kanellakis Theory and Practice Award.

- Mahadev Satyanarayanan was named a University Professor.

- Samarth Gupta gave a talk on "Correlated Multi-armed Bandits with a Latent Random Source" at ICASSP 2020. At the same conference, Jianyu Wang presented 2 papers: "Overlap Local-SGD: An Algorithmic Approach to Hide Communication Delays in Distributed SGD" and "Lookahead Converges to Stationary Points of Smooth Non-Convex Functions."

- The Allen Newell Award for Research Excellence winners include Lorrie Cranor, Lujo Bauer, and PDL Alumna Michelle Mazurek.

- Conglong Li defended his dissertaion on "Learned Adaptive Accuracy-Cost Optimization for Machine Learning Systems."

#### April 2020

- Jianyu Wang presented "SlowMo: Improving Communication-Efficient Distributed SGD with Slow Momentum" at ICLR 2020: The International Conference on Learning Representations.

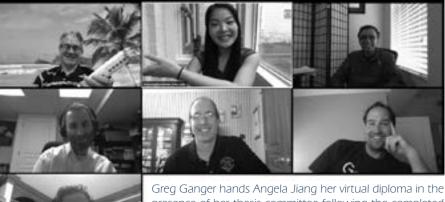

- Angela Hao Jiang defended her dissertation on "Improving Deep Learning Training and Inference

with Dynamic Hyperparameter Optimization."

- Sol Boucher proposed his PhD research on "Lightweight Preemptible Functions."

- Charles McGuffey proposed his PhD thesis topic on "Modernizing Models and Management of the Memory Hierarchy for Non-Volatile Memory."

- Rajat Kateja defended his dissertation on "Reducing Performance Overhead of Direct Access NVM Storage Redundancy."

#### March 2020

- Elliot Lockerman presented "Livia: Data-Centric Computing Throughout the Memory Hierarchy" at ASPLOS '20.

- "Writeback-Aware Caching," by Nathan Beckmann, Phillip B. Gibbons, Bernhard Haeupler, and Charles McGuffey won Best Paper at APOCS'20 in Salt Lake City, UT.

- Rashmi Vinayak won an NSF CA-REER Award.

- Michael Kuchnik gave his speaking skills talk on "Progressive Compressed Records: Taking a Byte out of Deep Learning Data."

#### February 2020

- Daniel Berger co-authored "Learning Relaxed Belady for Content Distribution Network Caching" for NSDI '20 in Santa Clara, CA.

- Pratik Fegade gave a presentation on "Scalable Pointer Analysis of Data Structures using Semantic Models" at the 29th Conference on Compiler Construction (CC '20) in San Diego, CA, USA.

- Rashmi Vinayak won a Facebook Distributed Systems Research Award.

- Andrew Chung proposed his PhD research on "Realizing Value in Shared Compute Infrastructures."

continued on page 33

## **RECENT PUBLICATIONS**

#### More IOPS for Less: Exploiting Burstable Storage in Public Clouds

Hojin Park, Gregory R. Ganger, George Amvrosiadis

12th USENIX Workshop on Hot Topics in Cloud Computing (HotCloud '20). Virtual Boston, MA, July 13-14, 2020.

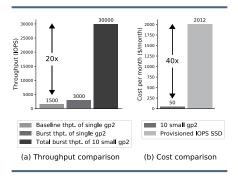

Burstable storage is a public cloud feature that enhances cloud storage volumes with credits that can be used to boost performance temporarily. These credits can be exchanged for increased storage throughput, for a short period of time, and are replenished over time. We examine how burstable storage can be leveraged to reduce cost and/ or improve performance for three use cases with different data-longevity requirements: traditional persistent storage, caching, and ephemeral storage. Although cloud storage volumes are typically priced by capacity, we find that each AWS gp2 volume starts with the same number of burst credits. Exploiting that fact, we find that aggressive interchanging of large numbers of small short-term volumes can increase IOPS by up to 100 at a cost increase of only 10-40%. Compared to an AWS ioI volume provisioned for the same performance, such interchanging reduces cost by 97.5%.

Throughput comparison (left) of three storage configurations of the same cost. 10 small gp2 volumes provide  $20 \times$  more IOPS (during burst) than a single volume. Purchasing this throughput directly increases cost by  $40 \times$  (right).

#### DriftSurf: A Risk-competitive Learning Algorithm under Concept Drift

Ashraf Tahmasbi, Ellango Jothimurugesan, Srikanta Tirthapura, Phillip B. Gibbons

International Conference on Machine Learning (ICML) 2020. Virtual Vienna, Austria, July 12-18, 2020.

When learning from streaming data, a change in the data distribution, also known as concept drift, can render a previously-learned model inaccurate and require training a new model. We present an adaptive learning algorithm that extends previous drift-detectionbased methods by incorporating drift detection into a broader stable-state/ reactivestate process. The advantage of our approach is that we can use aggressive drift detection in the stable state to achieve a high detection rate, but mitigate the false positive rate of standalone drift detection via a reactive state that reacts quickly to true drifts while eliminating most false positives. The algorithm is generic in its base learner and can be applied across a variety of supervised learning problems. Our theoretical analysis shows that the risk of the algorithm is competitive to an algorithm with oracle knowledge of when (abrupt) drifts occur. Experiments on synthetic and real datasets with concept drifts confirm our theoretical analysis.

### Order-Preserving Key Compression for In-Memory Search Trees

Huanchen Zhang, Xiaoxuan Liu, David G. Andersen, Michael Kaminsky, Kimberly Keeton, Andrew Pavlo

SIGMOD'20, June 14–19, 2020. Virtual Portland, OR.

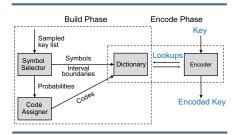

We present the High-speed Order-Preserving Encoder (HOPE) for in-memory search trees. HOPE is a fast dictionary-based compressor that encodes arbitrary keys while preserv-

The HOPE Framework – An overview of HOPE's modules and their interactions with each other in the two phases.

ing their order. HOPE's approach is to identify common key patterns at a fine granularity and exploit the entropy to achieve high compression rates with a small dictionary. We first develop a theoretical model to reason about order-preserving dictionary designs. We then select six representative compression schemes using this model and implement them in HOPE. These schemes make different tradeoffs between compression rate and encoding speed. We evaluate HOPE on five data structures used in databases: SuRF, ART, HOT, B+tree, and Prefix B+tree. Our experiments show that using HOPE allows the search trees to achieve lower query latency (up to 40% lower) and better memory efficiency (up to 30% smaller) simultaneously for most string key workloads.

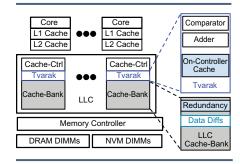

## TVARAK: Software-Managed Hardware Offload for Redundancy in Direct-Access NVM Storage

Rajat Kateja, Nathan Beckmann, Greg Ganger

47th International Symposium on Computer Architecture, May 30 – June 3, 2020, Virtual Valencia, Spain.

Production storage systems complement device-level ECC (which covers media errors) with system-checksums and cross-device parity. This systemlevel redundancy enables systems to detect and recover from data corruption due to device firmware bugs (e.g.,

## **RECENT PUBLICATIONS**

#### continued from page 5

TVARAK co-resides with the LLC bank controllers. It includes comparators to identify cache lines that belong to DAX-mapped pages and adders to compute checksums and parity. It includes a small on-controller redundancy cache that is backed by a LLC partition. TVARAK also stores the data diffs to compute checksums and parity.

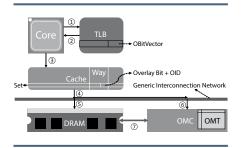

reading data from the wrong physical location). Direct access to NVM penalizes software-only implementations of system-level redundancy, forcing a choice between lack of data protection or significant performance penalties. We propose to offload the update and verification of system-level redundancy to TVARAK, a new hardware controller colocated with the last-level cache. TVARAK enables efficient protection of data from such bugs in memory controller and NVM DIMM firmware. Simulation-based evaluation with seven data-intensive applications shows that TVARAK is efficient. For example, TVARAK reduces Redis set-only performance by only 3%, compared to 50% reduction for a state-of-the-art software-only approach.

## Active Learning for ML Enhanced Database Systems

#### Lin Ma, Bailu Ding, Sudipto Das, Adith Swaminathan

#### SIGMOD'20, June 14–19, 2020. Virtual Portland, OR.

Recent research has shown promising results by using machine learning (ML) techniques to improve the performance of database systems, e.g., in query optimization or index recommendation. However, in many production deployments, the ML models' performance degrades significantly when the test data diverges from the data used to train these models.

In this paper, we address this performance degradation by using Binstances to collect additional data during deployment. We propose an active data collection platform, ADCP, that employs active learning (AL) to gather relevant data cost-effectively. We develop a novel AL technique, Holistic Active Learner (HAL), that robustly combines multiple noisy signals for data gathering in the context of database applications. HAL applies to various ML tasks, budget sizes, cost types, and budgeting interfaces for database applications. We evaluate ADCP on both industry-standard benchmarks and real customer workloads. Our evaluation shows that, compared with other baselines, our technique improves ML models' prediction performance by up to 2× with the same cost budget. In particular, on production workloads, our technique reduces the prediction error of ML models by 75% using about 100 additionally collected queries.

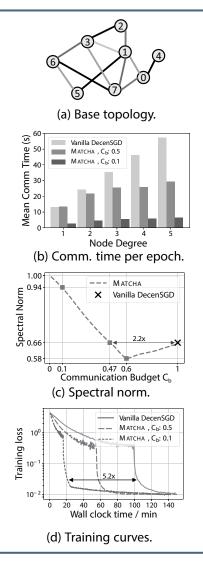

# Machine Learning on Volatile Instances

#### Xiaoxi Zhang, Jianyu Wang, Gauri Joshi, Carlee Joe-Wong

IEEE Intl. Conf. on Computer Communications (INFOCOM). Virtual Toronto, Canada, July 6-9, 2020.

Due to the massive size of the neural network models and training datasets used in machine learning today, it is imperative to distribute stochastic gradient descent (SGD) by splitting up tasks such as gradient evaluation across multiple worker nodes. However, running distributed SGD can be prohibitively expensive because it may require specialized computing resources such as GPUs for extended periods of time. We propose costeffective strategies that exploit volatile cloud instances that are cheaper than standard instances, but may be interrupted by higher priority workloads. To the best of our knowledge, this work is the first to quantify how variations in the number of active worker nodes (as a result of preemption) affects SGD convergence and the time to train the model. By understanding these tradeoffs between preemption probability of the instances, accuracy, and training time, we are able to derive practical strategies for configuring distributed SGD jobs on volatile instances such as Amazon EC2 spot instances and other preemptible cloud instances. Experimental results show that our strategies achieve good training performance at substantially lower cost.

#### Simple Near-Optimal Scheduling for the M/G/1

Ziv Scully, Mor Harchol-Balter, Alan Scheller-Wolf

Proceedings of the ACM Measurement and Analysis of Computer Systems -SIGMETRICS, June 2020, Boston, MA.

We consider the problem of preemptively scheduling jobs to minimize mean response time of an M/G/Iqueue. When we know each job's size, the shortest remaining processing time (SRPT) policy is optimal. Unfortunately, in many settings we do not have access to each job's size. Instead, we know only the job size distribution. In this setting the Gittins policy is known to minimize mean response time, but its complex priority structure can be computationally intractable. A much simpler alternative to Gittins is the shortest expected remaining processing time (SERPT) policy. While SERPT is a natural extension of SRPT to unknown job sizes, it is unknown whether or not SERPT is close to optimal for mean response time.

We present a new variant of SERPT called monotonic SERPT (M-SERPT) which is as simple as SERPT but has provably near-optimal mean response time at all loads for any job size distri-

bution. Specifically, we prove the mean response time ratio between M-SERPT and Gittins is at most 3 for load  $\rho \le 8/9$  and at most 5 for any load. This makes M-SERPT the only non-Gittins scheduling policy known to have a constant-factor approximation ratio for mean response time.

### Improving Approximate Nearest Neighbor Search through Learned Adaptive Early Termination

#### Conglong Li, Minjia Zhang, David G. Andersen, Yuxiong He

#### SIGMOD '20, June 14–19, 2020, Virtual Portland, OR, USA.

In applications ranging from image search to recommendation systems, the problem of identifying a set of "similar" real-valued vectors to a query vector plays a critical role. However, retrieving these vectors and computing the corresponding similarity scores from a large database is computationally challenging. Approximate nearest neighbor (ANN) search relaxes the guarantee of exactness for efficiency by vector compression and/or by only searching a subset of database vectors for each query. Searching a larger subset increases both accuracy and latency. State-of-the-art ANN approaches use fixed configurations that apply the same termination condition (the size of subset to search) for all queries, which leads to undesirably high latency when trying to achieve the last few percents of accuracy. We find that due to the index structures and the vector distributions, the number of database vectors that must be searched to find the ground-truth nearest neighbor varies widely among queries. Critically, we further identify that the intermediate search result after a certain amount of search is an important runtime feature that indicates how much more search should be performed.

To achieve a better tradeoff between latency and accuracy, we propose a novel approach that adaptively determines search termination conditions for individual queries. To do so, we build and train gradient boosting decision tree models to learn and predict when to stop searching for a certain query. These models enable us to achieve the same accuracy with less total amount of search compared to the fixed configurations. We apply the learned adaptive early termination to state-of-the-art ANN approaches, and evaluate the end-to-end performance on three million to billion-scale datasets. Compared with fixed configurations, our approach consistently improves the average end-to-end latency by up to 7.1 times faster under the same high accuracy targets. Our approach is open source at github.com/efficient/ faisslearned-termination.

### Overlap Local-SGD: An Algorithmic Approach to Hide Communication Delays in Distributed SGD

#### Jianyu Wang, Hao Liang, Gauri Joshi

International Conference on Acoustics, Speech, and Signal Processing (ICASSP) 2020. Virtual Barcelona, Spain, May 4-8, 2020.

Distributed stochastic gradient descent (SGD) is essential for scaling the machine learning algorithms to a large number of computing nodes. However, the infrastructures variability such as high communication delay or random node slowdown greatly impedes the performance of distributed SGD algorithm, especially in a wireless system or sensor networks. In this paper, we propose an algorithmic approach named Overlap-Local-SGD (and its momentum variant) to overlap the communication and computation so as to speedup the distributed training procedure. The approach can help to mitigate the straggler effects as well. We achieve this by adding an anchor model on each node. After multiple local updates, locally trained models will be pulled back towards the synchronized

anchor model rather than communicating with others. Experimental results of training a deep neural network on CIFAR-10 dataset demonstrate the effectiveness of Overlap-Local-SGD. We also provide a convergence guarantee for the proposed algorithm under non-convex objective functions.

#### Lookahead Converges to Stationary Points of Smooth Non-Convex Functions

#### Jianyu Wang, Vinayak Tantia, Nicolas Ballas, Michael Rabbat

ICASSP 2020: 45th International Conference on Acoustics, Speech, and Signal Processing. Virtual Barcelona, Spain, May 4-8, 2020.

The Lookahead optimizer [Zhang et al., 2019] was recently proposed and demonstrated to improve performance of stochastic firstorder methods for training deep neural networks. Lookahead can be viewed as a two time-scale algorithm, where the fast dynamics (inner optimizer) determine a search direction and the slow dynamics (outer optimizer) perform updates by moving along this direction. We prove that, with appropriate choice of step-sizes, Lookahead converges to a stationary point of smooth non-convex functions. Although Lookahead is described and implemented as a serial algorithm, our analysis is based on viewing Lookahead as a multi-agent optimization method with two agents communicating periodically.

# Correlated Multi-armed Bandits with a Latent Random Source

#### Samarth Gupta, Gauri Joshi, Osman Yagan

International Conference on Acoustics, Speech, and Signal Processing (ICASSP) 2020. Virtual Barcelona, Spain, May 4-8, 2020.

We consider a novel multi-armed bandit framework where the rewards

#### July 2020 David O'Hallaron Awarded the Philip L. Dowd Fellowship

Congratulations to ECE and CS Professor David O'Hallaron, who has been awarded the Philip L Dowd Fellowship in the College of

Engineering. The fellowship is awarded to recognize educational contributions and encourage the undertaking of an educational project such as textbook writing, educational technology development, laboratory experience improvement, educational software, or course and curriculum development. The Dowd Fellowship Award usually consists of a memento and a discretionary fund to support the nominee's education project and lasts for one year beginning the January following the award.

## July 2020 A New PDL Grandchild!

Welcome to Olivia Mae Losi, Karen Lindenfelser's fourth grandchild! Olivia was welcomed by Laura and Pete and sisters Layla and Nora, on July 23, 2020. She arrived at II:38 am; 6 lbs. I3 ounces and 20 inches, a bundle of indescribable joy!

#### June 2020 Best Paper at SIGMETRICS'20!

Congratulations to Ankur Mallick, Malhar Chaudhari, Ganesh Palanikumar, Utsav Sheth, and Gauri Joshi on receiving the best paper award at the Association for Computing Machinery's (ACM) annual SIGMETRICS conference, which was held virtually in Boston, MA, June 8-12. Their paper, "Rateless Codes for Near-Perfect Load Balancing in Distributed Matrix-Vector Multiplication," proposes a rateless fountain coding strategy that its latency is asymptotically equal to ideal load balancing, and it performs asymptotically zero redundant computation.

### May 2020 Phil Gibbons Named Recipient of 2019 Paris Kanellakis Theory and Practice Award

The Paris Kanellakis Theory and Practice Award honors specific theoretical accomplishments that have had a significant and demonstrable

effect on the practice of computing. This award is accompanied by a prize of \$10,000 and is endowed by contributions from the Kanellakis family, with additional financial support provided by ACM's Special Interest Groups on Algorithms and Computational Theory (SIGACT), Design Automaton (SIGDA), Management of Data (SIG-MOD), and Programming Languages (SIGPLAN), the ACM SIG Projects Fund, and individual contributions.

ACM has named Noga Alon of Princeton University and Tel Aviv University; Phillip Gibbons of Carnegie Mellon University; Yossi Matias of Google and Tel Aviv University; and Mario Szegedy of Rutgers University recipients of the ACM Paris Kanellakis Theory and Practice Award for seminal work on the foundations of streaming algorithms and their application to large-scale data analytics.

Alon, Gibbons, Matias and Szegedy pioneered a framework for algorithmic treatment of streaming massive datasets. Today, their sketching and streaming algorithms remain the core approach for streaming big data and constitute an entire subarea of the field of algorithms. Additionally, the concepts of sketches and synopses that they introduced are now routinely used in a variety of data analysis tasks in databases, network monitoring, usage analytics in internet products, natural language processing and machine learning.

In their seminal paper, "The Space Complexity of Approximating the Frequency Moments," Alon, Matias and Szegedy laid the foundations of the analysis of data streams using limited memory. Follow-up papers, including "Tracking Join and Selfjoin Sizes in Limited Storage," by Alon, Gibbons, Matias, and Szegedy, and "New Sampling-Based Summary Statistics for Improving Approximate Query Answers," by Gibbons and Matias, expanded on the idea of data synopses and were instrumental n the development of the burgeoning fields of streaming and sketching algorithms. This work has been applied to query planning and processing in databases and the design of small synopses to monitor vast quantities of data generated in networks.

-- acm.org news, May 2020

#### May 2020 M. Satyanarayanan Named A University Professor

Seven Carnegie Mellon University faculty members have been elevated to the rank of University Professor, the highest distinction a faculty member can achieve at CMU. Among the newly

## AWARDS & OTHER PDL NEWS

#### continued from page 8

appointed University Professors is Mahadev Satyanarayanan, a faculty member of the PDL.

"University Professors are distinguished

by international recognition and for their contributions to education, artistic creativity and/or research," said Provost Jim Garrett. "Each University Professor exemplifies a high level of professional achievement and an exceptional commitment to academic excellence at our university." Garrett said professors are nominated and recommended by academic leaders and faculty who have already achieved the designation of University Professor.

Mahadev Satyanarayanan, best known as Satya, is the Carnegie Group Professor of Computer Science. He is an experimental computer scientist, who designs, implements and evaluates systems. Satya's multi-decade research career has focused on the challenges of performance, scalability, availability and trust in information systems that reach from the cloud to the mobile edge of the Internet.

In the course of this work, he has pioneered many advances in distributed systems, mobile computing, pervasive computing, and the Internet of Things (IoT). Examples include his work as principal architect of CMU's pioneering Andrew File System in the 1980s, his work on disconnected and weakly connected mobile data access in the Coda File System in the early 1990s, his work on adaptive and energy-efficient mobile computing in the Odyssey system in the late 1990s and early 2000s and his most recent work in establishing the field of edge computing.

Satya earned his Ph.D. in computer science at CMU in 1983. An Association for Computing Machinery (ACM) and IEEE Fellow, he is the recipient of numerous awards, including the Association for Computing Machinery's prestigious Software System Award for his work on the Andrew File System.

-- with info from CMU News, May 15, 2020

### May 2020 Congratulations to 2020 SCS Faculty Award Winners!

Congratulations to these Allen Newell Award for Research Excellence winners: Lujo Bauer, Nicolas Christin, Lorrie Cranor, Saranga Komanduri, Michelle Mazurek, William Melicher, Sean Segretti, Rich Shay and Blase Ur, for their pioneering contribution to the science of evaluating password strength and for embodying this science in online tools that enable individuals and groups to more easily secure their systems.

-- Cylab News, May 22, 2020

### March 2020 Rashmi Vinayak Wins NSF CAREER Award

Rashmi Vinayak, an assistant professor in the Carnegie Mellon University Computer Science Department, has won a five-year, \$650,000 Fac-

ulty Early Career Development (CA-REER) Award, the National Science Foundation's most prestigious award for young faculty members.

The award will support Vinayak's work to improve the resource and energy efficiency of large-scale data centers, which together serve as the backbone for internet-based services, cloud services and data analytics platforms.

"Such large-scale systems are prone to failures and unavailability, and therefore have a high degree of redundancy built in to them to provide resilience against such events," she noted. "While redundancy provides resilience, it comes with a significant overhead in terms of resource and energy requirements. The overarching goal of this project is to design resource- and energy-efficient redundancy algorithms for data centers using tools based on information theory and coding theory."

Vinayak earned her Ph.D. in electrical engineering and computer science at the University of California at Berkeley, where she also worked as a postdoctoral researcher before joining CSD in 2017. Her previous awards include the Eli Jury Award from Berkeley's EECS Department, a Google Faculty Research Award, Facebook Communications and Networking Research Award, and the Tata Institute of Fundamental Research Memorial Lecture Award.

-- Carnegie Mellon University News, March 20, 2020

#### March 2020 APOCS'20 Best Paper!

The inaugural APOCS (SIAM Symposium on Algorithmic Principles of Computer Systems), held in January in Salt Lake City, UT, awarded its best paper accolades to a CMU team for continued on page 10

Chad Dougherty attending to the equipment in the DCO during the quarantine.

the paper "Writeback-Aware Caching", by Nathan Beckmann, Phillip B. Gibbons, Bernhard Haeupler, and Charles McGuffey. The paper explores the Writeback-Aware Caching problem, which modifies traditional caching problems by explicitly accounting for the cost of writing modified data back to memory on eviction. Congratulations!

## February 2020 Rashmi Vinayak Wins Facebook Distributed Systems Research Award

Congratulations to Rashmi on receiving a Facebook Distributed Systems Research Award for her work on "Reduced cost cluster storage by exploiting disk-reliability heterogeneity."

Facebook launched the Distributed Systems Award at the Symposium on Operating Systems Principles in October 2019 to foster forward-looking research in the area of distributed systems, applying important techniques from the field at Facebook's scale and sharing our designs, implementations, insights, and data with the community.

Out of a total of 63 proposals from 12 countries and 50 universities, eight winners were selected and are listed below. "We were thrilled to receive so many high-quality and thought-provoking submissions; we continue to be inspired by the work of our academic peers," says PDL Alumni Justin Meza, Research Scientist on the Facebook Core Systems team.

"It was challenging to only select eight awardees," he says. "We are grateful to the research community for engaging so enthusiastically with us, and we look forward to our continued collaboration." The RFP winners are invited to the Core Systems Faculty Summit in 2020 (time TBD), where they will have the opportunity to discuss their proposals with the research community.

--with info from Facebook Research News, Feb. 2020

## February 2020 Welcome Isaac

Huanchen Zhang and his wife would like us to meet their first child, Isaac Zhang who was born February 26, 2020, at 3:28pm, weighing 6lb 8oz, and measuring 18.5" long. Mom and baby are healthy, He has already melted their hearts! Life is a miracle!

January 2020 Juncheng (Jason) Yang Receives Facebook Fellowship

Four Ph.D. candidates in the School of Computer Science are among 36 outstanding students in computer science and engineering from

16 universities who have been named 2020 recipients of the Facebook Fellowship Program.

Each Facebook fellow receives tuition and fees for up to two academic years and a stipend of \$42,000, which includes conference travel support. Facebook received applications from 1,876 students at more than 100 universities for this year's program.

Among the four CMU students receiving the award is Juncheng Yang, a Ph.D. student in the Computer Science Department, to be a fellow in computer storage and efficiency. Yang is broadly interested in the reliability, performance and availability in the storage and caching subsystems of internet-scale web services.

--CMU School of Computer Science News, Jan. 29, 2020

### January 2020 Rashmi Vinayak Receives Prof. R. Narasimhan Memorial Lecture Award

Assistant Professor Rashmi Vinayak received the "Prof. R. Narasimhan memorial lecture award 2020" from Tata Institute of Fundamental Research (TIFR), which is a premier research institution in India. She delivered the memorial lecture at TIFR on January 6th 2020 concerning her work on "Convertible codes: New class of codes for efficient conversion of coded data in distributed storage."

She leads the CMU TheSys research group, which is a part of the Parallel Data Lab (PDL). Rashmi's research interests lie in the broad area of computer and networked systems with a current focus on reliability, availability, scalability, and performance challenges in data storage and caching systems, in systems for machine learning and in live video streaming.

## January 2020 Mor Harchol-Balter Awarded Bruce J. Nelson Chair in Computer Science

Congratulations to Mor, who was awarded the Dr. Bruce J. Nelson Professorship in Computer Science.

The chair was created by the family and friends of Bruce Nelson (CS'8I) in 2000, in his memory, to support a faculty member in the School of Computer Science.

October 2019 DeltaFS Project Takes Home R&D 100 Award

The R&D World Magazine an-

nounced its 100 winners for 2019

## **AWARDS & OTHER PDL NEWS**

#### continued from page 10

on October 29. "These 100 winning products and technologies are the disruptors that will change industries and make the world a better place in the coming years," said Paul J. Heney, Vice President, Editorial Director for R&D World. In the IT/Elec-

trical category, the winner is the CMU/Los Alamos National Laboratory collaborative project "DeltaFS—Rapidly Searching Big Data." Congratulations to its may contributors, including Brad Settlemyer, Scientist, Los Alamos National Laboratory; George Amvrosiadis, Research Professor Carnegie Mellon University; Gary Grider, HPC Division Director, Los Alamos National Laboratory; Qing Zheng, Research Assistant, Carnegie Mellon University; Greg Ganger, Jatras Professor, Carnegie Mellon University; Charles Cranor, Systems Scientist, Carnegie Mellon University; and Garth Gibson, Professor, Carnegie Mellon University

--RDWorld Online, October 29, 2019

#### September 2019 Abutalib Aghayev Awarded Hima and Jive Graduate Fellowship

Congratulations to Talib on receiving the Hima and Jive Fellowship this year! An anonymous donor established the Hima and Jive

Fellowship in Computer Science for International Students in 2012 to sup-

port one third-year graduate student annually in the Computer Science Department who has a permanent residence outside the United States, regardless of their national origin. This fellowship is to encourage students to overcome challenges and to have fun doing it. The fellowship is given to one international student in the School of Computer Science annually.

### October 2019 Welcome Clara!

INSERT INTO people (name, sex, dob, mother, alleged\_father) VALUES ('Clara X Pavlo', 'F', '2019-10-24', @DeepGenes, @andy\_pavlo);

## September 2019 Beckmann Earns NSF Early CAREER Award

Nathan Beckmann, an assistant professor in the Computer Science Department, has received a Faculty Early Career Development Award, the NSF's most prestigious award for young faculty members.

Nathan Beckmann, an assistant professor in the Computer Science Department, has received a five-year, roughly \$500,000 Faculty Early Career Development (CAREER) Award, the National Science Foundation's most prestigious award for young faculty members. Beckmann's research interests include computer architecture and performance modeling. The NSF grant will support his work crafting

and evaluating a new computer system design that makes accessing data faster and cheaper. Beckmann said more energy efficiency is needed to sustain growth in computing power for machine learning, social networking and robotics.

Applications currently have no control over how data is managed because memory hierarchy is fixed in hardware and hidden from software, resulting in unnecessary data movement. Beckmann's project will develop a new hardware-software co-design, wherein the operating system and hardware will collaboratively schedule tasks and data to improve efficiency.

Beckmann will involve high school, undergraduate and graduate students in research. He will also organize research workshops for undergraduate women and a summer internship program for underrepresented minorities.

Beckmann earned his master's degree and Ph.D. from the Massachusetts Institute of Technology, where he spent one year post-doc in the Computer Science and Artificial Intelligence Lab.

-- SCS News - September 12, 2019

#### April 2019

### Schwedock receives NSF Graduate Research Fellowship

Brian Schwedock, an electrical and computer engineering Ph.D. student, has received the prestigious National Science Foundation (NSF) Graduate Research Fellowship for his work in computer architecture and computer systems with a focus on caching.

## AWARDS & OTHER PDL NEWS

#### continued from page 11

Schwedock's current project improves the performance and energy efficiency of chip-multiprocessors in data centers. Data centers waste significant amounts of hardware, energy, and capital by isolating applications with different priorities, specifically latency-critical applications and batch applications.

"My project proposes an operating system runtime which reduces this waste by intelligently sharing hardware caches among these different

applications," says Schwedock. "Our results show major improvements in performance and energy efficiency for low priority batch applications while still meeting strict deadlines required by high priority latency-critical applications." The NSF Graduate Research Fellowship Program recognizes and supports outstanding graduate students in NSF-supported science, technology, engineering, and mathematics disciplines who are pursuing researchbased Master's and doctoral degrees at accredited United States institutions.

Schwedock is advised by Nathan Beckmann, assistant professor in the Computer Science Department.

Congratulations are also due to Giulio Zhou, who received an honorable mention for the NSF Graduate Research Fellowship Program this year.

-- ECE News and Events - April 18, 2019

### In Memoriam David B. Anderson

We were deeply saddened by the passing in October 2019 of one of PDL's foremost industry supporters. Dave Anderson's career with Seagate Technology in Shakopee, MN as Director of Strategic Planning and as Technologist spanned almost 40 years and

he participated in the PDL Retreats from almost the beginning. He is remembered by all in the PDL for his insight and encouragement of our research. For many of us, he will also be missed at other industry/university connection-points (FAST leadership meetings, as guest lecturer in our storage systems class, etc.). Dave's unique combination of a dry sense of humor and breadth of knowledge, both inside and outside our industry, are very much missed, but we are all better for having known him.

## **BETTER SCHEDULING IN DATA LAKES**

https://www.pdl.cmu.edu/DataLake/

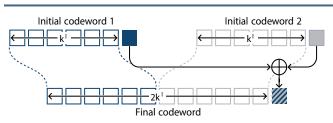

Andrew Chung, Subru Krishnan\*, Konstantinos Karanasos\*, Carlo Curino\*, Greg Ganger; \*Microsoft

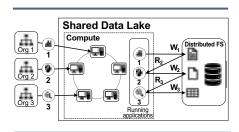

Shared data analytics infrastructures or "data lakes" have become core elements of modern data-driven enterprises, providing required data storage and analysis infrastructure (see Fig. 1). Data lakes enhance data processing via a combination of two critical properties: (i) a highly consolidated, multi-tenant infrastructure that enables multiple teams of data scientists and engineers to share resources, and (ii) easy data sharing between users and various types of data analytics applications. These properties increase data re-use and reduce overall computational resource-hours consumed.

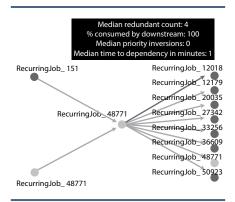

This data and resource sharing also creates a new challenge: hidden interjob dependencies. We say that Job B depends on Job A if Job B takes as input any output file generated and stored into a shared distributed file system by Job A. If Job C depends on Job B, it follows that it also has an (indirect) dependency on Job A. We refer to these as hidden dependencies, in contrast with explicit computation DAGs managed by schedulers within workflow managers or DBMSs, because no indication of such dependencies is available in job submissions.

Tracking data provenance and data movement both within the data lake and external components create an unprecedented opportunity to uncover and exploit these inter-job dependencies. As a case study, we analyzed petabytes of job and data provenance logs for 90 days of a 50k+ server cluster at Microsoft shared by over 1300 users from more than 150 internal organizations covering over

Figure 1: Data lake overview. Different types of applications, submitted by different organizations, share the same compute infrastructure and read (R) and write (W) to the same storage system, thereby creating inter-job dependencies as jobs consume the output of other jobs. For example, Job 2 (from Org 2) reads a file written by Job 1, so Job 2 depends on Job 1.

4 million submitted jobs and their 16 million inter-job dependencies. Almost 80% of the submitted jobs depended on output generated by at least one other

job. Many of the dependencies were shown as cross-organization, with 20% of jobs depending on jobs submitted by another organization.

Despite so much inter-job dependence, systems provide little support for addressing associated challenges. For example, even in the expertly-managed data lake we studied, different users and organizations make their own decisions regarding when to submit jobs and how to set job priorities. We found that 34% of recurring jobs played a submissiontiming game, where they are submitted without checking if job inputs they depend on are available, failing immediately if they are not.

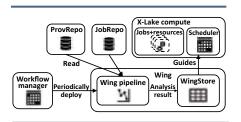

In response, we have developed the Wing dependency profiler, which efficiently processes historical job and provenance data to predict the impact of each new job on future jobs and user downloads. Although it is inherently difficult to know what future jobs will depend on the output generated by a current job, Wing finds success by focusing on recurrence.

Previous workload studies have shown that most jobs in data analytics environments are recurrent. Our analysis finds that inter-job dependency patterns are similarly recurrent, with jobs of the same template following similar input dependency patterns. There-

Figure 2: Wing architecture. The workflow manager periodically deploys Wing's analysis pipeline to X-Lake. Upon pipeline completion, results of its analyses are loaded in to WingStore, which informs Wing-guided schedulers with job and dependency characteristics.

fore, Wing is able to use historically recurring dependencies to (i) analyze and predict relationships between common, dependent recurring jobs, and (ii) guide a cluster scheduler to value jobs in a way that accounts for hidden dependencies.

Pairing Wing with traditional YARN scheduling replaces user-provided priorities with what Wing believes is a job's aggregate value. Experiments showed that inter-job dependencyaware guidance from Wing enables attainment of up to 66% more value compared to the default priority-based scheduling policy used in our data lake under cluster capacity crunch. We also found that when organizational cluster resource boundaries are removed, a Wing-guided scheduler can attain up to 93% of total value while using only 20% of total cluster capacity. In simulations driven by real job logs, a traditional YARN scheduler that uses Wing-provided values in place of userspecified priorities extracts more value (in terms of successful dependent jobs and user downloads) from a heavilyloaded cluster. By relying completely on Wing for guidance, YARN can achieve nearly IOO% of the value with 80% fewer machines, a 4X improvement over user-provided priorities and organizational queues.

Companies are always seeking to make the most out of infrastructure investments. Compute-hungry and opportunistic applications such as parameter exploration for machine learning are becoming more popular. This creates the opportunity and need for more sophisticated schedulers that can identify which jobs are the most consequential. Similarly, as operators become more efficient in operating clusters, unexpected global events (such as COVID-19) push infrastructures in to uncharted territories. Evaluation of job importance becomes key, and we find that guidance from Wing can help schedulers achieve higher value in the face of increasing amounts of resource demand, without requiring the deployment of significantly more compute resources.

## THE CASE FOR CUSTOM STORAGE BACKENDS IN DISTRIBUTED STORAGE SYSTEMS

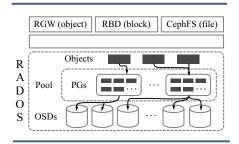

#### Abutalib Aghayev, Sage Weil, Michael Kuchnik, Mark Nelson, Gregory R. Ganger, George Amvrosiadis

Distributed file systems aggregate storage space from multiple physical machines into a single unified data store that offers high-bandwidth and parallel I/O, horizontal scalability, fault tolerance, and strong consistency. While distributed file systems may be designed differently and use unique terms to refer to the machines managing data placement on physical media, the storage backend is usually defined as the software module directly managing the storage device attached to physical machines. In these systems, the storage backend is the software module that manages space on disks (OSTs, Bricks, OSDs) attached to physical machines (OSSs, Nodes).

For a decade, the Ceph distributed file system followed the conventional wisdom of building its storage backend on top of local file systems. This is a preferred choice for most distributed file systems today, because it allows them to benefit from the convenience and maturity of battle-tested code. Ceph's experience, however, shows that this comes at a high price. Three recurring challenges arose. First, developing a zero-overhead transaction mechanism is challenging. Second, metadata performance at the local level can signifi-

## **STORAGE BACKENDS**

#### continued from page 13

cantly affect performance at the distributed level. Third, supporting emerging storage hardware is painstakingly slow.

#### **BLUESTORE**

In 2015, the Ceph project started designing and implementing BlueStore, a user space storage backend that stores data directly on raw storage devices and metadata in a key-value store. By taking full control of the I/O path, BlueStore has been able to efficiently implement full data checksums, inline compression, and fast overwrites of erasure-coded data, while also improving performance on common customer workloads. With this control, for example, BlueStore can choose the checksum block size based on the I/O hints, and if the hints indicate that objects are to be compressed, then a checksum can be computed after the compression, significantly reducing the total size of checksum metadata.

To achieve fast metadata operations, it stores metadata in RocksDB. To avoid consistency overhead, BlueStore writes data directly to raw disk, resulting in one cache flush for data write. Then, RocksDB is updated to reuse WAL files as a circular buffer, resulting in one cache flush for metadata write. For incoming writes larger than a minimum allocation size (64 KiB for HDDs, 16 KiB for SSDs), the data are written to a newly allocated extent.

BlueStore's full I/O control also allows it to provide an efficient clone operation. A clone operation simply

Fig. 1. High-level depiction of Ceph's architecture. A single pool with 3× replication is shown. Therefore, each placement group (PG) is replicated on three OSDs.

increments the reference count of dependent extents, and writes are directed to new extents. The same primitive also allows BlueStore to avoid journal double writes for object writes and partial overwrites that are larger than the minimum allocation size. For writes smaller than the minimum allocation size, both data and metadata are first inserted to RocksDB as promises of future I/O, and then asynchronously written to disk after the transaction commits. This deferred write mechanism has two purposes. First, it batches small writes to increase efficiency, because new data writes require two I/O operations whereas an insert to RocksDB requires one. Second, it optimizes I/O based on the device type; 64-KiB (or smaller) overwrites of a large object on an HDD are performed asynchronously in place to avoid seeks during reads, whereas in-place overwrites only happen for I/O sizes less than 16 KiB on SSDs.

Supporting Shingled Magnetic Recording (SMR) hard disks, which increase drive capacities by partially overlapping adjacent magnetic tracks, is also important for scale-out distributed file systems, because it lowers storage costs. Since BlueStore offers us the freedom to explore novel interfaces and data layouts, we looked toward adopting HM-SMR drives with the new zone interface and as a first step, we adapt RocksDB, an LSM-Tree instance, to run on zoned drives [2].

#### **SUMMARY**

Our experience with Ceph shows the belief that developing a mature, productionready storage backend from scratch is a time-consuming process is inaccurate. Furthermore, we find that developing a special-purpose, user space storage backend from scratch (I) reclaims the significant performance left on the table when building a backend on a general-purpose file system, (2) makes it possible to adopt novel, backward incompatible storage hardware, and (3) enables new features by gaining complete control of the I/O stack.

Jason Boles keeps all the technical aspects of the 2019 PDL Retreat running smoothly.

In only two years since its inception, BlueStore outperformed previous established backends and is adopted by 70% of users in production. By running in user space and fully controlling the I/O stack, it has enabled spaceefficient metadata and data checksums. fast overwrites of erasure-coded data, inline compression, decreased performance variability, and avoided a series of performance pitfalls of local file systems. Finally, it makes the adoption of backward-incompatible storage hardware possible, an important trait in a changing storage landscape that is learning to embrace hardware diversity. For more information, please see the SOSP 2019 paper [1].

#### REFERENCES

[I] File Systems Unfit as Distributed Storage Backends: Lessons from 10 Years of Ceph Evolution. A. Aghayev, S. Weil, M. Kuchnik, M. Nelson, G.R. Ganger, G. Amvrosiadis. SOSP '19, October 27–30, 2019, Huntsville, ON, Canada. https://www.pdl.cmu. edu/PDL-FTP/Storage/ceph-expsosp19\_abs.shtml

[2] Reconciling LSM-Trees with Modern Hard Drives using BlueFS. A. Aghayev, S. Weil, G.R. Ganger, G. Amvrosiadis. Carnegie Mellon University Parallel Data Lab Technical Report CMU-PDL-19-102, April 2019. https://www.pdl.cmu.edu/PDL-FTP/ FS/CMU-PDL-19-102\_abs.shtml

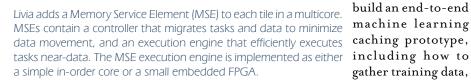

Erasure codes are popular tools for imparting resilience to data unavailability while remaining agnostic to the cause of unavailability and using less resources than replication-based approaches. These properties have led to the wide adoption of erasure codes in storage and communication systems. An erasure code encodes k data units to produce r redundant "parity" units in such a way that any k of the total (k + r) data and parity units are sufficient for a decoder to recover the original k data units. The overhead incurred by an erasure code is ((k+r)/k), which is typically much less than that of replication.

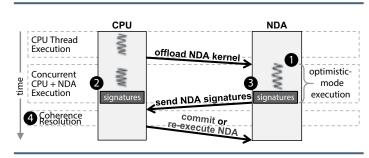

A number of recent works have studied the theoretical aspects of using erasure codes for alleviating the effects of slowdowns and failures that occur in distributed computation. This setup, called "coded computation," uses erasure coding to recover the outputs of a deployed computation over data units. In coded computation, data units are encoded into parity units, and the deployed computation is performed over all data and parity units in parallel. A decoder then uses the outputs from the fastest k of these computations to reconstruct the outputs corresponding to the original data units. For a prediction-serving system, employing coded computation would involve encoding queries such that a decoder can recover slow or failed predictions.

The primary differences between coded computation and the traditional use of erasure codes in storage and communication come from (I) performing computation over encoded data and (2) the need for an erasure code to recover the results of computation over data units rather than the data units themselves. Whereas traditional applications of erasure codes involve encoding data units and decoding from a subset of data and parity units, in coded computation one decodes by using the output of computation over data and parity units. This difference calls for fundamentally rethinking the design of erasure codes, as many of the erasure codes which have been widely used in storage and communication are applicable only to a highly restricted class of computations.

As erasure codes can correct slowdowns with low latency and require less resource-overhead than replicationbased approaches, enabling the use of coded computation in predictionserving systems has potential for efficient mitigation of tail latency inflation. However, the complex nonlinear components common to popular machine learning models, such as neural networks, make it challenging to design effective coded-computation solutions for prediction-serving systems. Existing coded-computation approaches, which focus on handcrafting new erasure codes, can support only rudimentary computations, rendering them inadequate for prediction-serving systems.

We propose to overcome the challenges of employing coded computation for prediction-serving systems via a learning-based approach. We show that machine learning can eschew the difficulty of hand-crafting codes and enable coded computation over neural network inference. However, this approach requires careful consideration: we show that simply replacing encoders and decoders with machine learning models limits opportunities to reduce tail latency.

Motivated by these insights, we take a fundamentally new approach to coded computation by introducing new components that we call "parity models." A parity model is a neural network trained to convert encoded queries into a form that enables decoding of unavailable predictions. Unlike conventional coded-computation approaches, which design new erasure codes, parity models enable the use of simple, fast encoders and decoders, such as addition and subtraction. Compared to learning encoders and decoders, this new approach reduces the computational burden introduced on a prediction-serving system's frontend, and also reduces the latency of reconstructions. We implement parity models in ParM, a prediction-serving system designed to make use of erasure-coded resilience. ParM encodes multiple queries together into a parity query, and a deployed parity model transforms the parity query such that its output enables a decoder to reconstruct slow or failed predictions.

The predictions returned by ParM are the same as those returned by any prediction-serving system in the absence of slowdowns and failures. When slowdowns and failures do occur, the output of ParM's decoder is an approximate reconstruction of a slow or failed prediction. Reconstructing approximations of unavailable predictions is appropriate for inference, as predictions themselves are approximate, and because ParM's reconstructions are returned only when a prediction would otherwise be slow or failed. In this scenario, it is often preferable to return an approximate prediction rather than a late one.

We evaluate the accuracy of ParM's reconstructions on a variety of neural networks and inference tasks such as image classification, speech recognition, and object localization. We also evaluate ParM's ability to reduce tail latency in the presence of resource contention. ParM reconstructs unavailable predictions with high accuracy and reduces tail latency while using 2-4× less additional resources than replication-based approaches. For example, using only half of the additional resources as replication, ParM's reconstructions from ResNet-18 models on various tasks are within a 6.5% difference in accuracy compared to if the original predictions were not slow or failed. Furthermore, ParM brings tail latency up to 3.5× closer to median latency, while maintaining the same median. This enables ParM to maintain predictable latencies in the face of slowdowns and failures. These results show the promise of learningbased coded computation to open new doors for imparting efficient resilience to prediction-serving systems.

### DISSERTATION ABSTRACT: Learned Adaptive Accuracy-Cost Optimization for Machine Learning Systems

#### Conglong Li Carnegie Mellon University, SCS

#### PhD Defense — May 1, 2020

This dissertation seeks to address the challenge of making adaptive accuracycost balancing inside systems for largescale machine learning-based recommendation services. We show that it is important to make performance tradeoff decisions at a per-query basis instead of a predefined policy for all queries. We show that we can achieve a better tradeoff between accuracy and cost by leveraging lightweight machine learning models to make more adaptive decision-making inside systems infrastructure.

Large-scale recommendation services have two computation-heavy components with strict accuracy and latency targets: scoring (typically achieved by complex machine learning models) and candidate retrieval (typically achieved by approximate nearest neighbor search). We first introduce a caching system for scoring component in recommendation systems (in particular search advertising systems). Inside the cache, we leverage light-

Rajat Kateja at his desk at home after delivering his dissertation defense remotely in May.

weight machine learning models to make adaptive cache refresh decisions, which provides a better balance between recommendation accuracy and computation cost. This leads to a better net profit in the search advertising context. We then present the learned adaptive termination for approximate nearest neighbor search inside the candidate retrieval component. We leverage lightweight machine learning models to decide how much to search for each query, which provides a better balance between the search accuracy and latency (computation cost).

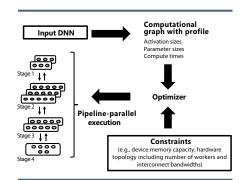

## DISSERTATION ABSTRACT: Improving Deep Learning Training and Inference with Dynamic Hyperparameter Optimization

Angela Hao Jiang Carnegie Mellon University, SCS

PhD Defense — April 29, 2020

Over the past decade, deep learning has demonstrated high accuracy on challenges in fields like computer vision and natural language processing, revolutionizing these fields in the process. Deep learning models are now a fundamental building block for applications such as autonomous driving, medical imaging, and machine translation. However, many challenges remain when deploying these models in production. Researchers and practitioners must address a diversity of questions, including how to efficiently design, train, and deploy resourceintensive deep learning models and how to automate these approaches while ensuring robustness to changing conditions.

Our work aims to improve the efficiency of deep learning training and inference, as well as the underlying systems' robustness to changes in the environment. We address these issues by focusing on the many hyperparameters that are tuned to optimize the model's accuracy and resource us-

age. These hyperparameters include the choice of model architecture, the training dataset, the optimization algorithm, the hyperparameters of the optimization algorithm (e.g., the learning rate and momentum) and the training time budget. Currently, in practice, almost all hyperparameters are tuned once before training and held static. This is sub-optimal as the conditions that dictate the best hyperparameter value change over time (e.g., training progress, inference hardware). We apply dynamic tuning to hyperparameters that have traditionally been considered static. Using three case studies, we show that using runtime information to dynamically adapt hyperparameters that are traditionally static, such as the emphasis on individual training examples and the weights updated during transfer learning, can increase the efficiency of deep learning training and inference.

## DISSERTATION ABSTRACT: Reducing Performance Overhead of Direct Access NVM Storage Redundancy

Rajat Kateja Carnegie Mellon University, ECE

#### PhD Defense — April 10, 2020

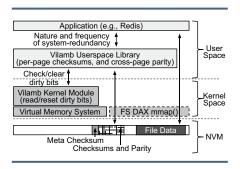

Non-volatile memory (NVM) based storage is poised for mainstream deployment. DIMM form-factor NVM devices reside on the memory bus and offer DRAM-like access granularities and latencies along with non-volatility. NVM's Direct Access (DAX) interface enables applications to map persistent data into their address space and access it with load and store instructions, eliminating system software overheads.

Production deployment of DAX NVM storage would require that the storage system offer resilience against firmware-bug-induced data corruption, akin to conventional storage systems. Protection against firmware-buginduced data corruptions requires

the storage system to maintain systemlevel redundancy, which we refer to as system-redundancy. With DAX interfacing, the lack of interposed system software makes it challenging to identify data reads and writes that should trigger system-redundancy verification and updates, respectively. Further, the DAX granularities (e.g., 64-byte cache lines) are incongruent with typical system-redundancy granularities (e.g., 4K pages), leading to high performance overhead in maintaining system-redundancy.

This dissertation demonstrates that DAX NVM storage systems can efficiently maintain system-redundancy by relaxing the data coverage guarantees or by leveraging a hardware offload. We support the thesis with two case studies: Vilamb and Tvarak.

The Vilamb library maintains systemredundancy asynchronously, avoiding critical path interpositioning and amortizes the overhead of system redundancy updates across multiple writes to a page. As a result, Vilamb provides 3 -5× the throughput of the state-of-the-art software solution at high operation rates. For applications that need system-redundancy with high performance, and can tolerate some delaying of data redundancy, Vilamb provides a tunable knob between performance and time-to-coverage. Even with the delayed coverage, Vilamb increases the mean time to data loss due to firmware-induced corruptions by up to two orders of magnitude in comparison to maintaining no system-redundancy.

Tvarak is a software-managed hardware offload to efficiently maintain systemredundancy for direct-access (DAX) NVM storage. Tvarak reconciles the mismatch between DAX granularities and typical system-redundancy granularities by introducing cache-line granular checksums (only) for DAXmapped data. Tvarak also uses caching to reduce the number of extra NVM accesses for maintaining and verifying system-redundancy. Applications' data access locality leads to reuse of systemredundancy that Tvarak leverages with a small dedicated on-controller cache and configurable LLC partitions. Simulation-based evaluation demonstrates Tvarak's efficiency. For example, Tvarak reduces Redis setonly performance by only 3%.

#### DISSERTATION ABSTRACT: Enhancing Programmability, Portability, and Performance with Rich Cross-Layer Abstractions

Nandita Vijaykumar Carnegie Mellon University, ECE

PhD Defense — October 11, 2019

Programmability, performance portability, and resource efficiency have emerged as critical challenges in harnessing complex and diverse architectures today to obtain high performance and energy efficiency. While there is abundant research, and thus significant improvements, at different levels of the stack that address these very challenges, in this thesis, we observe that we are fundamentally limited by the interfaces and abstractions between the application and the underlying system/hardware-specifically, the hardware-software interface. The existing narrow interfaces poses two critical challenges. First, significant effort and expertise are required to write highperformance code to harness the full potential of today's diverse and sophisticated hardware. Second, as a hardware/ system designer, architecting faster and more efficient systems is challenging as the vast majority of the program's semantic content gets lost in translation with today's application-system interfaces. Moving towards the future, these challenges in programmability and efficiency will be even more intractable as we architect increasingly heterogeneous and sophisticated systems.

This thesis makes the case for rich lowoverhead cross-layer abstractions as a highly effective means to address the above challenges. These abstractions are designed to communicate higherlevel program information from the application to the underlying system and hardware in a highly efficient manner, requiring only minor additions to the existing interfaces. In doing so, they enable a rich space of hardware-software cooperative mechanisms to optimize for performance. We propose 4 different approaches to designing richer abstractions between the application, system software, and hardware architecture in different contexts to significantly improve programmability, portability, and performance in CPUs and GPUs: (i) Expressive Memory: A unifying crosslayer abstraction to express and communicate higher-level program semantics from the application to the underlying system/architecture to enhance memory optimization; (ii) The Locality Descriptor: A cross-layer abstraction to express and exploit data locality in GPUs; (iii) Zorua: A framework to decouple the programming model from management of on-chip resources and parallelism in GPUs; (iv) Assist Warps: A helper-thread abstraction to dynamically leverage underutilized compute/memory bandwidth in GPUs to perform useful work. In this thesis, we present each concept and describe how communicating higherlevel program information from the application can enable more intelligent resource management by the architecture and system software to significantly improve programmability, portability, and performance in CPUs and GPUs.

## DISSERTATION ABSTRACT: Memory-Efficient Search Trees for Database Management Systems

Huanchen Zhang Carnegie Mellon University, SCS

PhD Defense — October 4, 2019

The growing cost gap between DRAM and storage together with increasing database sizes means that database management systems (DBMSs) now operate with a lower memory to storage size ratio

## **DEFENSES & PROPOSALS**

#### continued from page 17

than before. On the other hand, modern DBMSs rely on in-memory search trees (e.g., indexes and filters) to achieve high throughput and low latency. These search trees, however, consume a large portion of the total memory available to the DBMS. This dissertation seeks to address the challenge of building compact yet fast in-memory search trees to allow more efficient use of memory in data processing systems. We first present techniques to obtain maximum compression on fast read-optimized search trees. We identified sources of memory waste in existing trees and designed new succinct data structures to reduce the memory to the theoretical limit. We then introduce ways to amortize the cost of modifying static data structures with bounded and modest cost in performance and space. Finally, we approach the search tree compression problem from an orthogonal direction by building a fast order-preserving key compressor. Together, these three pieces form a practical recipe for achieving memory-efficiency in search trees and in DBMSs.