AN INFORMAL PUBLICATION FROM ACADEMIA'S PREMIERE STORAGE SYSTEMS RESEARCH CENTER DEVOTED TO ADVANCING THE STATE OF THE ART IN STORAGE AND INFORMATION INFRASTRUCTURES.

## CONTENTS

| Recent Publications I   |

|-------------------------|

| Director's Letter2      |

| Year in Review4         |

| PDL News & Awards8      |

| New PDL Faculty II      |

| Defenses & Proposals 12 |

| PDL Alumni News28       |

## PDL CONSORTIUM MEMBERS

| Amazon                     |

|----------------------------|

| Google                     |

| Hewlett Packard Enterprise |

| Hitachi, Ltd.              |

| IBM Research               |

| Intel Corporation          |

| Meta                       |

| Microsoft Research         |

| NetApp, Inc.               |

| Oracle Corporation         |

| Pure Storage               |

| Salesforce                 |

| Samsung Semiconductor Inc. |

| Two Sigma                  |

| Western Digital            |

## **RECENT PUBLICATIONS**

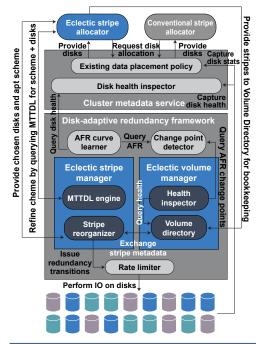

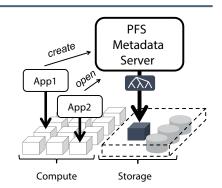

### **Tiger: Disk-Adaptive Redundancy Without Placement Restrictions**

Saurabh Kadekodi, Francisco Maturana, Sanjith Athlur, Arif Merchant, K. V. Rashmi, Gregory R. Ganger.

Proceedings of the 16th USENIX Symposium on Operating Systems Design and Implementation (OSDI), July 11–13, 2022. Carlsbad, CA, USA.

Large-scale cluster storage systems use redundancy (via erasure coding) to ensure data durability. Diskadaptive redundancy-dynamically tailoring the redundancy scheme to observed disk failure rates—promises significant space and cost savings. Existing disk-adaptive redundancy systems, however, pose undesirable constraints on data placement, partitioning disks into subclusters that have homogeneous failure rates and forcing each erasure-coded stripe to be entirely placed on the disks within one subcluster. This design increases risk, by reducing intra-stripe diversity and being more susceptible to unanticipated changes in a make/model's failure rate, and only works for very large storage clusters fully committed to disk-adaptive redundancy.

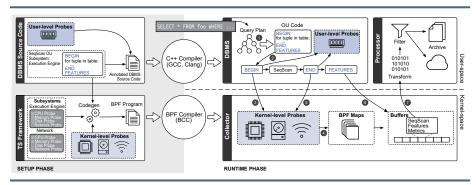

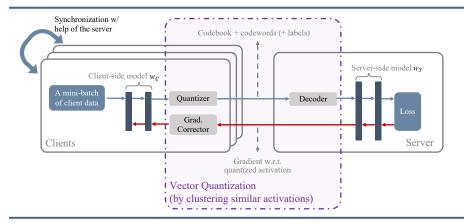

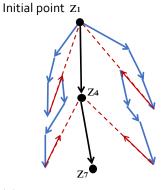

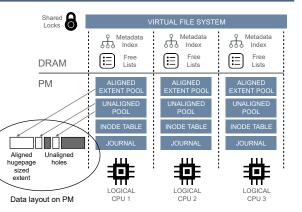

Architecture of Tiger. The blue boxes correspond to Tiger's components. The gray boxes correspond to existing components in cluster storage system architecture and components present in existing disk-adaptive redundancy systems.

Tiger is a new disk-adaptive redundancy system that efficiently avoids adoptionblocking placement constraints, while also providing higher space-savings and lower risk relative to prior designs. To do so, Tiger introduces the eclectic stripe, in which redundancy is tailored to the potentially-diverse failure rates of whichever disks are selected for storing that particular stripe. With eclectic stripes, preexisting placement policies can be used while still enjoying the space-savings and robustness benefits of disk-adaptive redundancy. This paper introduces eclectic striping and Tiger's design, including a new mean-time-to-data-loss (MTTDL) approximation technique and new approaches for ensuring safe per-stripe settings given that failure rates of different devices change over time. In addition continued on page 5

#### FROM THE DIRECTOR'S CHAIR

## GREG GANGER

At risk of jinxing things: we're back! We didn't get to do a PDL Retreat in Fall 2021, as we had hoped and planned, but we did an in-person PDL Visit Day in May 2022 and are

fully on track for a full PDL Retreat in November 2022. We are very excited to get back to gathering in-person regularly to interact, share, brainstorm, and collaborate.

It has been an amazing year for PDL, on the research and student accomplishment fronts, despite the life challenges from which we are all emerging. Indeed, PDL researchers were recognized, over and over, with an unprecedented run of Best Paper awards (OSDI 2021, NSDI 2021, SOSP 2021, Eurosys 2022, ASPLOS 2022)... and Rashmi won the VMware Systems Award, George and team won an R&D100 award, and there were several other awards and nominations as well. Behind the awards, of course, has been great progress on many fronts and new projects/collaborations initiated. A highlight has been strong continued interaction with PDL sponsors, including cool guest lectures to PDL's storage systems and cloud classes and co-authored papers (including some of the awards) with us in the context of research collaborations. I will not try to cover all of the PDL progress across storage systems, database systems, ML systems, and data processing infrastructurespecifics can be found throughout the newsletter-but I will briefly highlight a few things.

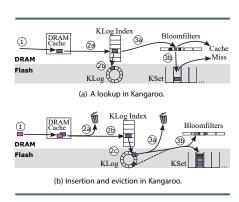

I'll start with caching and storage systems, where great research results and awards have arisen from our collaborations with companies. As one example, the Kangaroo Flash cache design enables unprecedented efficiency for Flash caching of small objects... and was presented as Best Paper at SOSP 2021. As another, the SegCache memory cache designs enables unprecedented scalability for in-memory key-value caching... and was presented as Best Paper at NSDI 2021. The disk-adaptive redundancy project has created a new flexible way to work with existing data-placement policies and achieve even bigger capacity-reduction benefits for cluster storage systems; the flexible HPC storage project's microservice-based approach received an R&D100 award; there are cool new software designs for emerging device interfaces (e.g., ZNS) and for emerging smart storage devices; etc. We thank our PDL sponsor companies who have enabled (and collaborated on) much of the research mentioned above by allowing us to experiment with real devices, workload traces, and failure logs!

We also continue our extensive work in large-scale data processing systems, including systems for ML and schedulers for analytics clusters. For example, the Pollux scheduler for shared GPU clusters co-adaptively makes resource assignment decisions and job configuration decisions (e.g., batch size) for DNN-training jobs to achieve unprecedented ef-

### THE PDL PACKET

#### THE PARALLEL DATA LABORATORY

School of Computer Science Department of ECE Carnegie Mellon University 5000 Forbes Avenue Pittsburgh, PA 15213-3891 VOICE 412•268•6716

#### PUBLISHER

Greg Ganger

#### EDITOR

Joan Digney

The PDL Packet is published once per year to update members of the PDL Consortium. A pdf version resides in the Publications section of the PDL Web pages and may be freely distributed. Contributions are welcome.

#### THE PDL LOGO

Skibo Castle and the lands that comprise its estate are located in the Kyle of Sutherland in the northeastern part of Scotland. Both 'Skibo' and 'Sutherland' are names whose roots are from Old Norse, the language spoken by the Vikings who began washing ashore regularly in the late ninth century. The word 'Skibo' fascinates etymologists, who are unable to agree on its original meaning. All agree that 'bo' is the Old Norse for 'land' or 'place,' but they argue whether 'ski' means 'ships' or 'peace' or 'fairy hill.'

Although the earliest version of Skibo seems to be lost in the mists of time, it was most likely some kind of fortified building erected by the Norsemen. The present-day castle was built by a bishop of the Roman Catholic Church. Andrew Carnegie, after making his fortune, bought it in 1898 to serve as his summer home. In 1980, his daughter, Margaret, donated Skibo to a trust that later sold the estate. It is presently being run as a luxury hotel.

### **PARALLEL DATA** LABORATORY

#### FACULTY

Greg Ganger (PDL Director) 412•268•1297 ganger@ece.cmu.edu

George Amvrosiadis Gauri Joshi David Andersen Todd Mowry Nathan Beckmann Chuck Cranor Lorrie Cranor Christos Faloutsos Phil Gibbons Mor Harchol-Balter Zhihao Jia

David O'Hallaron Andy Pavlo Majd Sakr M. Satyanarayanan Dimitrios Skarlatos Akshitha Sriraman Rashmi Vinayak

#### STAFF MEMBERS

Bill Courtright, 412 • 268 • 5485 (PDL Executive Director) wcourtright@cmu.edu Karen Lindenfelser, 412•268•6716 (PDL Administrative Manager) karen@ece.cmu.edu Jason Boles Joan Digney Chad Dougherty Mitch Franzos Baljit Singh

#### **VISITING RESEARCHERS &** POST DOCS

Andrew Crotty

#### **GRADUATE STUDENTS**

| Nikhil Agarwal        | Wan Shen Lim        |

|-----------------------|---------------------|

| Daiyaan Arfeen        | Shouxu Lin          |

| Nikhil Arora          | Elliot Lockerman    |

| Sanjith Athlur        | Hao Yang Lu         |

| Nirav Atre            | Francisco Maturana  |

| Mohammad Bakhshalipo  | our Sara McAllister |

| Matt Butrovich        | Nj Mukherjee        |

| Zixu Chen             | Hojin Park          |

| Neville Chima         | Deepayan Patra      |

| Yae Jee Cho           | Xavier Ramos        |

| Val Choung            | Sumanth Rao         |

| Andrew Chung          | Brian Schwedock     |

| Pratik Fegade         | Shalini Shukla      |

| Samarth Gupta         | Suhas J Subramanya  |

| Eeshwar Gurushankar   | Minh Truong         |

| Travis Hance          | Jaylen Wang         |

| Garrison Hess         | Sherry Wang         |

| Ankush Jain           | Yuanxin Wang        |

| Jekyeom Jeon          | Ziqi Wang           |

| Ellango Jothimurugesa | n Daniel Wong       |

| Shantanu Kamath       | Mike Xu             |

| Akshath Karanam       | Jason Yang          |

| Thomas Kim            | Jiuzhi Yu           |

| Timothy Kim           | Will Zhang          |

| Jack Kosaian          | Kaiyang Zhao        |

| Joseph Koshakow       | Yiwei Zhao          |

| Michael Kuchnik       | Giulio Zhou         |

|                       |                     |

#### UNDERGRADUATE STUDENTS

Jonathan Chiu

## FROM THE DIRECTOR'S CHAIR

ficiency... and was presented as Best Paper at OSDI 2021. We are extending our recent work on how inter-job dependency information can be uncovered from provenance information and job logs to improve job shifting and scheduling that exploits intermittent resource availability (e.g., best effort resources and green energy). An emerging area of exploration is automated storage and caching configuration in cloud infrastructures to accommodate large-scale data processing within and across clouds. And, excitingly, broad aggregated activities are emerging among the research into simplifying, automating, and improving efficiency in big-data ML systems, both in collaboration with other CMU groups and with the Army's Pittsburgh-homed AI Integration Center (AI2C), as it looks to adopt and adapt key concepts into the new mechanisms they are building for AI development and use in the Army.

Database systems research continues strong, and the various approaches to automation are proving to be effective and impactful. The OtterTune service embodies blockbox approaches for database tuning and is part of a startup company, associated with a "music" release! The NoisePage DBMS embodies whitebox approaches, in which the DBMS is designed from the beginning to automatically adapt and is also emerging strong... and three researchers involved with it moved on to new faculty positions this summer!

Many other ongoing PDL projects are also producing cool results... too many for me to cover, especially as I strive to keep this note brief. But, this newsletter and the PDL website offer more details and additional research highlights.

I'm always overwhelmed by the accomplishments of the PDL students and staff, and it's a pleasure to work with them. As always, their accomplishments point at great things to come.

PDL Consortium members, guests and CMU students, staff and faculty gather for the opening poster session at the 2022 Spring Visit Day.

## July 2022

- Nirav Atre gave his speaking skills talk on "SurgeProtector: Mitigating Temporal Algorithmic Complexity Attacks using Adversarial Scheduling."

- Saurabh Kadekodi presented "Tiger: Disk-Adaptive Redundancy Without Placement Restrictions" at OSDI '22 in Carlsbad, CA.

- Benjamin Samuel Berg defended his PhD thesis research on "A Principled Approach to Parallel Job Scheduling."

- Graham Gobieski defended his PhD thesis research on "Ultra-lowpower, Energy-minimal Computer Architectures."

#### June 2022

- Matthew Butrovich presented "Tastes Great! Less Filling! High Performance and Accurate Training Data Collection for Self-Driving Database Management Systems" at SIGMOD '22, in Philadelphia, PA.

- Brian C. Schwedock presented "täko: A Polymorphic Cache Hierarchy for General-Purpose Optimization of Data Movement" at ISCA '22, in New York, NY. Brian and his co-authors were nominated for best paper!

- Minh S. Q. Truong and Mohammad Bakhshalipour received an Apple Inc. Ph.D. Fellowship in Integrated Systems for 2021-2023. Minh interned this summer with

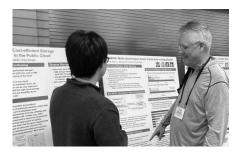

Hojin Park discusses his poster on "Mimir: Finding Cost-efficient Storage Configurations in the Public Cloud" with Tom Hicks of Microsoft Research.

the Neural Engine HW Architecture group at Apple Inc. under Jaewon Shin. Mohammad interned with Apple's Platform Architecture team in both 2021 and 2022.

#### May 2022

- 23rd Annual Spring Visit Day and Consortium Speaker Series!

- Michael Kuchnik proposed his PhD thesis research on "Beyond Model Efficiency: Data Optimizations for Machine Learning Systems."

- Thomas Sheek Kim proposed his PhD research topic "Leveraging Emerging Storage Technologies to Improve Performance, Reliability, and Availability."

#### April 2022

- Francisco Maturana gave his speaking skills talk on "Convertible Codes: Efficient Conversion of Coded Data in Distributed Storage."

- Sanjith Athlur and his co-authors won Best Paper at EuroSys'22 for their paper "Varuna: Scalable, Low-cost Training of Massive Deep Learning Models" in Rennes, France.

#### March 2022

- Yae Jee Cho, a member of Gauri Joshi's team, presented "Client Selection in Federated Learning: Convergence Analysis and Powerof-Choice Selection Strategies" at the AISTATS '22 virtual conference.

- Todd Mowry's 1992 Paper "Design and Evaluation of a Compiler Algorithm for Prefetching" was noted as Influential by ASPLOS'22.

- Ellango Jothimurugesan proposed his PhD research on "Large-scale Machine Learning over Streaming Data."

#### February 2022

Dimitrios Skarlatos and his coauthors won the Best Paper Award at ASPLOS '22 for their paper "TMO: Transparent Memory Offloading in Datacenters" in Lausanne, Switzerland.

Sol Boucher presented a defense of his PhD research on "Lightweight Preemptible Functions."

### January 2022

- Rashmi Vinayak received the 2021 VMware Systems Research Award for her work to enhance computer system reliability and efficiency by combining coding-theoretic algorithms, machine learning models and systems.

- Ellango Jothimurugesan gave his speaking skills talk on "DriftSurf: Stable-State / Reactive-State Learning under Concept Drift."

- Andrew Crotty presented "Are You Sure You Want to Use MMAP in Your Database Management System?" at CIDR '22 in Chaminade, CA.

#### December 2021

- Gauri Joshi's team presented "Leveraging Spatial and Temporal Correlations in Sparsified Mean Estimation" at the virtual NeurIPS '21 conference.

- Graham Gobieski proposed his PhD research on "Ultra-lowpower, Energy-minimal Computer Architectures."

#### November 2021

- The PDL paper "Heterogeneity and Dynamicity of Clouds at Scale: Google Trace Analysis," by Alexey Tumanov, Greg Ganger and coauthors won an ACM SoCC Test of Time Award.

- Jack Kosaian presented "Arithmetic-Intensity-Guided Fault Tolerance for Neural Network Inference on GPUs" at SC'21, in St. Louis, MO.

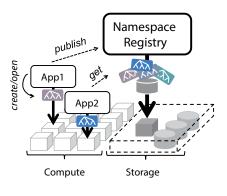

- Qing Zheng presented "DeltaFS: A Scalable No-Ground-Truth Filesystem For Massively-Parallel

#### continued from page 1

to avoiding placement constraints, evaluation with logs from real-world clusters shows that Tiger provides better space-savings, less bursty IO for changing redundancy schemes, and better robustness (due to increased risk-diversity) than prior disk-adaptive redundancy designs.

### Tastes Great! Less Filling! High Performance and Accurate Training Data Collection for Self-Driving Database Management Systems

Matthew Butrovich, Wan Shen Lim, Lin Ma, John Rollinson, William Zhang, Yu Xia, Andrew Pavlo

SIGMOD '22, June 12–17, 2022, Philadelphia, PA, USA.

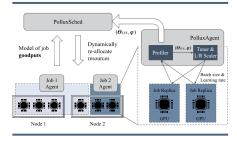

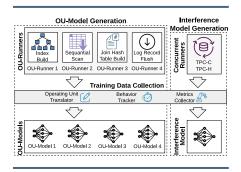

A self-driving database management system (DBMS) aims to configure, deploy, and optimize almost all aspects of itself automatically without human intervention or guidance. Achieving this high level of automation relies on machine learning (ML) models that predict how a DBMS will behave in different scenarios. This behavior encompasses all DBMS runtime operations, including query execution and maintenance tasks. These ML-based behavior models for a self-driving DBMS require low-level training data about a DBMS's internals. Such training data includes (I) features that describe the workload, environment, and DBMS configuration, and (2) both DBMS- and hardware-level metrics. But it is difficult to collect training data from a DBMS while it is running because it can introduce performance and measurement degradations that hinder the ML models' ability to predict the DBMS's behavior correctly.

We present the TScout (TS) framework for collecting training data from selfdriving DBMSs. Our framework is an internal approach where developers annotate a DBMS's source code with hooks to monitor the system's behavior. TS then extracts these hooks and

TScout's architecture is split into two phases. In the Setup Phase, a developer annotates the DBMS's source code. Then, TS uses code generation to create a customized Collector for the Runtime Phase when the Collector retrieves metrics and the DBMS's OU input features to create training data. Finally, data are shipped to the Processor for archiving with other training data. The DBMS is deployed together with TS on the same server. [1] The DBMS executes the query's plan. [2] The thread executes the OU for the annotated sequential scan. [3] When the DBMS encounters the BEGIN marker for this OU, it triggers TS to enable metrics collection using its probes. [4] The Collector uses a BPF map to store a snapshot of probe results at the BEGIN marker. [5] After completion of the OU and triggering the END marker, the Collector retrieves this data from the BPF map, invokes the necessary probes again to get a current snapshot, computes the value for each metric, and stores the final results back in the BPF map. When the DBMS reaches the OU's FEATURES marker, [6] the Collector packages the features and metrics together into a sample data point and [7] sends it to the Processor via a perf ring buffer.

generates a kernel-level program (via Linux's BPF) that efficiently captures metrics from multiple sources (e.g., CPU performance counters, memory allocators). TS combines these metrics with internal DBMS state observations, generating training data for behavior models. We integrated TS in a PostgreSQL-compatible DBMS and measured its ability to collect training data for both OLTP and OLAP workloads. Our results show that TS generates training data for a deployed DBMS to train more accurate models than previous methods with only a 7% performance reduction.

## täko : A Polymorphic Cache Hierarchy for General-Purpose Optimization of Data Movement

Brian C. Schwedock, Piratach Yoovidhya, Jennifer Seibert, Nathan Beckmann

ISCA '22, June 18–22, 2022, New York, NY, USA. Nominated for Best Paper!

Current systems hide data movement from software behind the load-store

interface. Software's inability to observe and respond to data movement is the root cause of many inefficiencies, including the growing fraction of execution time and energy devoted to data movement itself. Recent specialized memory-hierarchy designs prove that large data-movement savings are possible. However, these designs require custom hardware, raising a large barrier to their practical adoption.

This paper argues that the hardwaresoftware interface is the problem, and custom hardware is often unnecessary with an expanded interface. The täko architecture lets software observe data movement and interpose when desired. Specifically, caches in täkō can trigger software callbacks in response to misses, evictions, and writebacks. Callbacks run on reconfigurable dataflow engines placed near caches. Five case studies show that this interface covers a wide range of data-movement features and optimizations. Microarchitecturally, täkō is similar to recent near-data computing designs, adding  $\approx 5\%$  area to a baseline multicore. täkō improves performance by I.4×-4.2×,

#### continued from page 5

similar to prior custom hardware designs, and comes within 1.8% of an idealized implementation.

## Mimir: Finding Cost-efficient Storage Configurations in the Public Cloud

Hojin Park, Gregory R. Ganger, George Amvrosiadis

Carnegie Mellon University Parallel Data Lab Technical Report CMU-PDL-22-102, February 2022.

Public cloud providers offer a diverse collection of block storage options with different costs and performance SLAs. As a consequence, it is difficult to select the right allocations for storage backends when moving data-heavy applications to the cloud. Mimir is a tool for automatically finding a costefficient virtual storage cluster (VSC) configuration for a customer's storage workload and performance requirements. Importantly, since no single allocation type is best for all workloads, Mimir considers all allocation types and even heterogeneous mixes of them. In our experiments, compared to state-of-the-art approaches that consider only one allocation type, Mimir finds VSC configurations that reduce cost by up to 81% for substantial storage workloads.

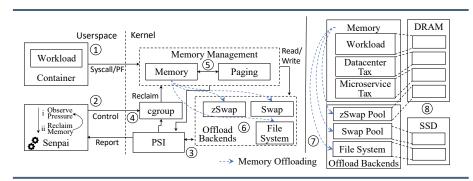

# TMO: Transparent Memory Offloading in Datacenters

Johannes Weiner, Niket Agarwal, Dan Schatzberg, Leon Yang, Hao Wang, Blaise Sanouillet, Bikash Sharma, Tejun Heo, Mayank Jain, Chunqiang Tang, Dimitrios Skarlatos

#### ASPLOS '22, February 28 – March 4, 2022, Lausanne, Switzerland. BEST PAPER AWARD!

The unrelenting growth of the memory needs of emerging datacenter applications, along with ever increasing cost and volatility of DRAM prices, has led to DRAM being a major infrastructure expense. Alternative technologies, such as NVMe SSDs and upcoming

Overview of the TMO architecture (left) and the memory and storage layout (right).

NVM devices, offer higher capacity than DRAM at a fraction of the cost and power. One promising approach is to transparently offload colder memory to cheaper memory technologies via kernel or hypervisor techniques. The key challenge, however, is to develop a datacenter-scale solution that is robust in dealing with diverse workloads and large performance variance of different offload devices such as compressed memory, SSD, and NVM.

This paper presents TMO, Meta's transparent memory offloading solution for heterogeneous datacenter environments. TMO introduces a new Linux kernel mechanism that directly measures in realtime the lost work due to resource shortage across CPU, memory, and I/O. Guided by this information and without any prior application knowledge, TMO automatically adjusts how much memory to offload to heterogeneous devices (e.g., compressed memory or SSD) according to the device's performance characteristics and the application's sensitivity to memory-access slowdown. TMO holistically identifies offloading opportunities from not only the application containers but also the sidecar containers that provide infrastructure-level functions. To maximize memory savings, TMO targets both anonymous memory and file cache, and balances the swap-in rate of anonymous memory and the reload rate of file pages that were recently evicted from the file cache.

TMO has been running in produc-

tion for more than a year, and has saved between 20-32% of the total memory across millions of servers in our large datacenter fleet. We have successfully upstreamed TMO into the Linux kernel.

## Client Selection in Federated Learning: Convergence Analysis and Power-of-Choice Selection Strategies

Yae Jee Cho, Jianyu Wang, Gauri Joshi

International Conference on Artificial Intelligence and Statistics (AISTATS), March 2022.

Federated learning is a distributed optimization paradigm that enables a large number of resource-limited client nodes to cooperatively train a model without data sharing. Several works have analyzed the convergence of federated learning by accounting of data heterogeneity, communication and computation limitations, and partial client participation. However, they assume unbiased client participation, where clients are selected at random or in proportion of their data sizes. In this paper, we present the first convergence analysis of federated optimization for biased client selection strategies, and quantify how the selection bias affects convergence speed. We reveal that biasing client selection towards clients with higher local loss achieves faster error convergence. Using this insight, we propose POWER-OF-CHOICE, a communication- and computationefficient client selection framework

that can flexibly span the trade-off between convergence speed and solution bias. Our experiments demonstrate that POWER-OF-CHOICE strategies converge up to 3 faster and give 10% higher test accuracy than the baseline random selection.

#### Adapting the RACER Architecture to Integrate Improved In-ReRAM Logic Primitives

Minh S. Q. Truong, Liting Shen, Alexander Glass, Alison Hoffmann, L. Richard Carley, James A. Bain, Saugata Ghose.

IEEE Journal on Emerging and Selected Topics in Circuits and Systems, Early Access, 12 May 2022.

Modern computing applications based upon machine learning can incur significant data movement overheads in state-of-the-art computers. Resistive-memory-based processingusing-memory (PUM) can mitigate this data movement by instead performing computation in situ (i.e., directly within memory cells), but device-level limitations restrict the practicality and/or performance of many PUM architecture proposals. The RACER architecture overcomes these limitations, by proposing efficient peripheral circuitry and the concept of bit-pipelining to enable high-performance, high-efficiency computation using small memory tiles. In this work, we extend RACER to adapt easily to different PUM logic families, by (I) modifying the device access circuitry to support a wide range of logic families, (2) evaluating three logic families proposed by prior work, and (3) proposing and evaluating a new logic family called OSCAR that significantly relaxes the switching voltage constraints required to perform logic with resistive memory devices. We show that the modified RACER architecture, using the OSCAR logic family, can enable practical PUM on real ReRAM devices while improving performance and energy savings by 30% and 37%, respectively, over the original RACER work.

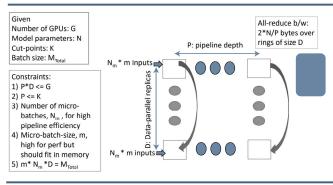

## Varuna: Scalable, Low-cost Training of Massive Deep Learning Models

Sanjith Athlur, Nitika Saran, Muthian Sivathanu, Ramachandran Ramjee, Nipun Kwatra

#### EuroSys '22, April 5-8, 2022, Rennes, France. BEST PAPER AWARD!

Systems for training massive deep learning models (billions of parameters) today assume and require specialized "hyperclusters": hundreds or thousands of GPUs wired with specialized high-bandwidth interconnects such as NV-Link and Infiniband. Besides being expensive, such dependence on hyperclusters and custom high-speed inter-connects limits the size of such clusters, creating (a) scalability limits on job parallelism; (b) resource fragmentation across hyperclusters.

In this paper, we present Varuna a new system that enables training massive deep learning models on commodity networking. Varuna makes thrifty use of networking resources and automatically configures the user's training job to efficiently use any given set of resources. Therefore, Varuna is able to leverage 'low-priority" VMs that cost about 5x cheaper than dedicated GPUs, thus significantly reducing the cost of training massive models. We demonstrate the efficacy of Varuna by training

massive models, including a 200 billion parameter model, on 5x cheaper lspot VMs", while maintaining high training throughput. Varuna improves end-toend training time for language models like BERT and GPT-2 by up to 18x compared to other model-parallel approaches and up to 26% compared to other pipeline parallel approaches on commodity VMs. The code for Varuna is available at https://github.com/microsoft/varuna.

### RAIZN: Redundant Array of Independent Zoned Namespaces

Thomas Kim, George Amvrosiadis, Jekyeom Jeon, Huaicheng Li, David G. Andersen, Greg Ganger, Michael Kaminsky, Matias Bjørling

Carnegie Mellon University Parallel Data Lab Technical Report CMU-PDL-22-101, January 2022.

Zoned Namespace (ZNS) SSDs are the most recent evolution of host-managed flash-based storage, enabling improved performance at a lower cost-per-byte compared to traditional block interface SSDs. To date, there is no support for arranging these new devices in redundant arrays (RAID), which may limit their deployment in environments where this is the favored mechanism for increasing reliability and throughput. This paper identifies key challenges in the design of a RAID-like mechanism for ZNS SSDs, such as the requirement to manage metadata updates and persist partial stripe writes in the absence of overwrite semantics in the device's interface. We present the design, implementation, and evaluation of RAIZN, a logical volume manager that exposes a ZNS interface and stripes data and parity across ZNS SSDs.

Varuna problem setting and constraints.

## July 2022 PDL Participates in CMU's Computer Science Scholars and Al4All Summer Programs

The CSS and AI4All @ Carnegie Mellon summer programs provide opportunities for students who have been historically excluded in STEM to study with full-time faculty, staff, and researchers who are leaders in the field. Students participated in project-based learning and attended lectures in various aspects of computing and artificial intelligence. They then applied those concepts and techniques to real world challenges and learn to leverage CS and AI for social good. Part of the 3-week residency for students attending these programs this year included a tour of the DCO with Jason Boles, Bill Courtright, Chuck Cranor, Mitch Franzos, and Greg Ganger.

### June 2022 Brian Schwedock and Coauthors Nominated for Best Paper at ISCA'22!

Congratulations to Brian Schwedock and his co-authors on the nomination of "täkō: A Polymorphic Cache Hierarchy for General-Pur-

pose Optimization of Data Movement" for Best Paper, presented at ISCA '22 in New York this June. täkō aims to improve software's ability to observe and respond to data movement, improving many inefficiencies, including the growing fraction of execution time and energy devoted to data movement itself.

## May 2022 Introducing Sanay Rashmi Shah!

We would like to welcome the newest member of the PDL! Sanay Rashmi Shah was born on May II, near midnight, weighing 5lb 1502. His big sister Aanya is very excited and likes to read him bedtime stories. Parents Rashmi and Nihar are thrilled!

## April 2022 Best Paper at EuroSys'22!

Congratulations to Sanjith Athlur, a new graduate student with the PDL, on achieving a Best Paper award at Eurosys 2022 for his work

on "Varuna: Scalable, Low-cost Training of Massive Deep Learning Models." Varuna makes thrifty use of available networking resources and automatically configures the user's training job in massive deep learning models to efficiently use any given set of resources, reducing the effects of scalability limits on job parallelism and resource fragmentation. Sanjith will be working toward his Ph.D. in Computer Science with Rashmi Vinayak and Greg Ganger.

## March 2022 1992 Paper Noted as Influential by ASPLOS'22

A 1992 paper written by Todd Mowry, PDL faculty and professor in the

Computer Science Department, and SCS alums Monica Lam and Anoop Gupta received an influential paper award at this year's Inter-

national Conference on Architectural Support for Programming Languages (ASPLOS). The paper, "Design and Evaluation of a Compiler Algorithm for Prefetching", proposed a compiler algorithm to insert prefetch instructions into code that operates on dense matrices.

-- SCS WEDNESDAY WIRE: March 30, 2022

## February 2022 Dimitrios Skarlatos and Collaborators Win Best Paper Award at ASPLOS '22!

Congratulations to Dimitrios Skarlotos, assistant professor in the Computer Science Department, for receiving a best paper award

for "TMO: Transparent Memory Offloading in Datacenters" at ASPLOS 2022. ASPLOS is the premier forum for interdisciplinary systems research, intersecting computer architecture, hardware and emerging technologies, programming languages and compilers, operating systems and networking.

-- SCS WEDNESDAY WIRE: March 9, 2022

## January 2022 Rashmi Vinayak Receives 2021 VMware Systems Research Award

Congratulations to Rashmi Vinayak, Assistant Professor of Electrical and Computer Engineering at CMU, on the occasion of her 2021 VMware Systems Research Award. The award

## PDL NEWS & AWARDS

is given in recognition of the originality, impact and future potential of Rashmi's research, which focuses on work to enhance com-

puter system reliability and efficiency by combining coding-theoretic algorithms, machine learning models and systems. See VMware's Award Announcement page for more details.

#### November 2021 PDL Paper wins ACM SoCC Test of Time Award!

The ACM SoCC 2021 test of time award goes to "Heterogeneity and Dynamicity of Clouds at Scale: Google Trace Analysis"! Congratulations to the authors Charles Reiss, Alexey Tumanov, Gregory R. Ganger, Randy H. Katz, and Michael A. Kozuch for their impactful work. The paper was first introduced at the 3rd ACM Symposium on Cloud Computing, held from October 14th-17th, 2012, in San Jose, CA. The paper helps its readers to better understand the challenges in developing effective cloudbased resource schedulers, analyzing the first publicly available trace data from a sizable multi-purpose cluster.

### October 2021 Sara McAllister and Colleagues Win Best Paper at SOSP'21!

Congratulations to Sara McAllister, Benjamin Berg, Julian Tutuncu-Macias, Juncheng Yang, Sathya Gunasekar, Jimmy Lu, Daniel Berger, Nathan Beckmann, and Gregory R. Ganger

on receiving the Best Paper Award at SOSP'21, which was held virtually in Germany. The paper "Kangaroo: Caching Billions of Tiny Objects

on Flash" introduces Kangaroo, a new flash-cache design that optimizes both DRAM usage and flash writes to maximize cache performance while minimizing cost.

### October 2021 Mochi Project Wins 2021 R&D 100 Award

Mochi is a state-of-the-art open source tool for rapid development of customized data services supporting highperformance computing, big data, and large-scale learning across many scientific fields. Mochi allows developing these distributed services with a relatively small amount of new code while still enabling very high performance. Mochi was co-developed by researchers from Argonne National Laboratory, Carnegie Mellon University (George Amvrosiadis, Chuck Cranor, Qing Zheng), and Los Alamos National Laboratory. Established in 1963, the R&D 100 Awards is the only S&T (science and technology) awards competition that recognizes new commercial products, technologies and materials for their technological significance that are available for sale or license.

July 2021 PDL Researchers Win Best Paper at OSDI'21!

Congratulations to Aurick Qiao, Sang Keun Choe, Suhas Jayaram Subramanya, Willie Neiswanger, Qirong Ho, Hao Zhang, Gregory R. Ganger, and Eric P. Xing, on being awarded one of three Best

Paper Awards at OSDI'21. The paper, "Pollux: Co-adaptive Cluster Scheduling for Goodput-Optimized Deep Learning," discusses improved scheduling performance in deep learning (DL) clusters by adaptively co-optimizing inter-dependent factors both at the per-job level and at the cluster-wide level.

## June 2021 Christos Faloutsos Promoted to University Professor

Congratulations to Christos, who

has been elevated to the rank of University Professor, the highest distinction a faculty member can achieve at CMU.

#### June 2021 Huaicheng Li Recognized as Distinguished Reviewer

Congratulations to Huaicheng,

who has been recognized as a Distinguished Reviewer for his service to Systor 2021, the 14th ACM International System and Storage Conference.

### May 2021 CMU Research Forms Basis for Automatic Database Tuning Service

Dana Van Aken's dissertation has been transformed into a service aimed at improving the databases that power

## PDL NEWS & AWARDS

#### continued from page 9

popular websites. She founded the company with her advisor, Andy Pavlo, and Bohan Zhang, who worked with Van

Aken and Pavlo as a research assistant.

OtterTune, a play on the once ubiquitous Auto-Tune, uses machine learning to automatically optimize databases, improving performance and efficiency and potentially saving companies time and money. Users could see faster loading times and improved services with a database humming along in the background. In case studies, the OtterTune improved efficiency by 33% to 50%, cut one company's costs in half, and saved another tens of thousands of dollars.

"There are hundreds of settings to consider when optimizing a database, too many for humans to properly tune," said Dana Van Aken, "Otter-Tune takes human trial and error out of the mix." And from Pavlo: "Database management systems now exceed the administrator's ability to optimize them. We've put years of research into solving this problem, which we know will lead to significant increases in efficiencies and cost savings for customers."

-- info from CMU SCS News Wednesday, May 12, 2021

### February 2021 Two Win Integrated Systems Apple Fellowship

Congratulations to Minh S.Q. Truong and Mohammad Bakhshalipour, who have both received an Apple PhD Fellowship in Integrated Systems for the 2021-2023 academic years! The award includes a stipend and internships with Apple during the summers covered by the award.

## **NEW PDL FACULTY**

#### **Zhihao Jia** Assistant Professor, CSD

the PDL! Zhihao is an assistant professor in the Computer Science Department at Carnegie Mellon Univer-

Welcome to

sity. Before joining CMU, he was a research scientist at Facebook from 2020-2021. He received his PhD from the Computer Science Department at Stanford University in 2020, where he was co-advised by Alex Aiken and Matei Zaharia. Before Stanford, Zhihao received his bachelor's degree in Computer Science from the Special Pilot CS Class supervised by Andrew Yao at Tsinghua University.

Zhihao is interested in building systems for emerging application domains such as machine learning, quantum computing, and large-scale data analytics. In particular, his current research focuses on accelerating deep learning computations on modern hardware platforms, and optimizing quantum computations on today's intermediate-scale quantum devices. He is actively looking for strong and self-motivated students interested in building systems for machine learning and quantum computing to join his group.

#### Akshitha Sriraman Assistant Professor, ECE

We would also like to welcome Akshitha Sriraman! She is an assistant professor in the Department of Electrical and Computer En-

gineering at Carnegie Mellon University. Her research interests are in the area of bridging computer architecture and software systems, with a focus on making hyperscale data centers more efficient (via solutions that span the systems stack). The central theme of her work is to design software that is aware of new hardware constraints/ possibilities and architect hardware that efficiently supports new hyperscale software requirements. She has recently been exploring ideas on designing "customized" hardware that can still generically support diverse applications, compiler-driven hardware design optimizations, novel software threading designs, and efficient I/O subsystems.

Akshitha's systems solutions to improve hardware efficiency have been deployed in real hyperscale data centers and currently serve billions of users, saving millions of dollars and meaningfully reducing the global carbon footprint. Additionally, her hardware design proposals have influenced the design of Intel's Alder Lake (Golden Cove and future generation) CPU architectures and its Infrastructure Processing Unit.

Akshitha's research has been recognized with an IEEE Micro Top Picks distinction and she was also awarded a Facebook Fellowship, a Rackham Merit Ph.D. Fellowship, and a CIS Full-Tuition Scholarship. She was selected to attend the Rising Stars in EECS Workshop and the Heidelberg Laureate Forum. She completed her Ph.D. in Computer Science and Engineering at the University of Michigan.

## DISSERTATION ABSTRACT: A Principled Approach to Parallel Job Scheduling

Benjamin Samuel Berg Carnegie Mellon University, SCS

#### PhD Defense —July 27, 2022

Parallelizable workloads are ubiquitous and appear across a diverse array of modern computer systems. Data centers, supercomputers, machine learning clusters, distributed computing frameworks, and databases all process jobs designed to be parallelized across many servers or cores. A job will receive some speedup from being parallelized across additional servers or cores, allowing the job to complete more quickly. However, jobs generally cannot be perfectly parallelized, and receive diminishing returns from being allocated additional cores. Hence, given a fixed number of cores, it is not obvious how to allocate cores across a set of jobs in order to reduce the response times of the jobs - the times from when each job arrives to the system until it is completed. While this question has been considered by the worst-case scheduling community, existing results are hampered by strong lower bounds on worst-case performance and tend to suggest policies which do not work well in practice. The goal of this thesis is to develop and analyze practical policies for scheduling parallelizable jobs using the tools of performance modeling and stochastic analysis.

PDL students and staff set up posters for the poster sessions at the 2022 PDL Spring Visit day.

Our approach in developing new scheduling policies for parallelizable jobs is threefold. First, we develop new stochastic models of parallelizable jobs running in a multicore system. Second, we analyze these new models using the tools of stochastic performance modeling, showing that a stochastic analysis emits scheduling policies which outperform the policies suggested by the worst-case literature. Finally, we validate our theoretical models through simulation and we develop new heuristic policies based on our theoretical results. We apply this methodology to a variety of practical settings where systems are required to schedule parallelizable jobs. We consider the case where job sizes are completely unknown to the system, the case where job sizes are perfectly known to the system, and the case where some jobs are known to be larger than others on average. Similarly, we consider the case where jobs are all assumed to have the same scaling behavior, the case where some jobs are more parallelizable than others, and the case where a job's parallelizability can change over time.

### DISSERTATION ABSTRACT: Ultra-low-power, Energyminimal Computer Architectures

Graham Gobieski Carnegie Mellon University, SCS

PhD Defense — July 12, 2022

Ultra-low-power (ULP) sensor devices are increasingly being deployed for a variety of use-cases that require sophisticated processing of sensed data. Regardless of the deployment, energy-efficiency is critical; for batterypowered devices, energy-efficiency determines device lifetime, while for energy-harvesting devices, energyefficiency determines performance by dictating the frequency of recharging. Unfortunately, existing devices pay a severe energy tax for their program-

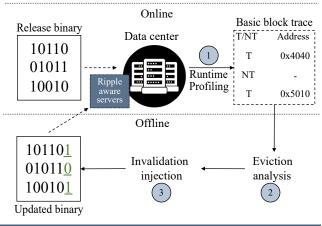

mability, wasting energy in instruction-fetch/decode, pipeline-control and data supply. Further, offloading computation from an edge-device to the cloud is not practical as communication costs an order of magnitude more energy than local compute. The solution is to re-design the ULP sensor system stack to increase the energy-efficiency of on-board compute and enable sophisticated processing of sensed data. This thesis proposes such a stack - from software to silicon - that leverages new execution models to reduce the tax of programmability and achieve extreme energy-efficiency. Specifically it contributes I) Sonic, a software framework that enables machine inference on intermittently-operating, energy-harvesting devices, 2) Manic, a vector-dataflow co-processor (and corresponding silicon prototype), 3) Snafu, an ULP coarse-grain-reconfigurable-array (CGRA) generation framework and architecture, and 4) RipTide, a co-designed dataflow compiler and energy-minimal CGRA. Sonic was the first demonstration of machine inference on an intermittent device, but also exposed the flaws of existing ULP devices. Manic fixed these problems by combining vector execution to amortize instruction fetch with dataflow execution to minimize data supply energy by forwarding intermediate values directly from producers to consumers. Snafu extended Manic's vector-dataflow to further reduce energy by minimizing the toggling of shared pipeline resources. Its generated CGRAs implement spatial-vector-dataflow execution that lays out computation across a fabric of PEs, keeping each PE configured in the same way throughout kernel execution. Finally, RipTide improves overall system efficiency by compiling and offloading to its CGRA, programs written in C with complex controlflow and irregular memory accesses. Together these contributions form the basis of a new ULP sensor system

continued on page 12

## **DEFENSES & PROPOSALS**

#### continued from page 11

stack that is > 2 orders of magnitude more efficient than existing systems, enabling new emerging applications that require intelligence "beyondthe-edge."

## DISSERTATION ABSTRACT: Lightweight Preemptible Functions

Sol Boucher Carnegie Mellon University, SCS

#### PhD Defense — February 24, 2022

We introduce novel programming abstractions for isolation of both time and memory. They operate at finer granularity than traditional primitives, supporting preemption at sub-millisecond timescales and tasks defined at the level of a function call. This resolution enables new functionality for application programmers, including users of unmanaged systems programming languages, all without requiring changes to the existing systems stack. Despite being concurrency abstractions, they employ synchronous invocation to allow application programmers to make their own scheduling decisions. However, we find that they compose naturally with existing concurrency abstractions centered around asynchronous background work, such as threads and futures. We demonstrate how such composition can enable asynchronous cancellation of threads and the implementation of preemptive thread libraries in userland, both regarded for decades as challenging problems.

#### DISSERTATION ABSTRACT: Towards Elastic and Resilient In-Network Computing

Daehyoek Kim Carnegie Mellon University, SCS

#### PhD Defense — October 1, 2021

Recent advances in programmable networking hardware technology such as programmable switches and network interface cards create a new computing paradigm called in-network computing. This new paradigm allows functionality that has been served by servers or proprietary hardware devices, ranging from network middleboxes to components of distributed systems, to now be performed in the network. The demand for higher performance and the commercial availability of programmable hardware have driven the popularity of in-network computing.

While many recent efforts have demonstrated the performance benefit of innetwork computing, we observe that there is still a huge gap between what it offers today and evolving application demands. In particular, we argue that in-network computing lacks resource elasticity and fault resiliency which are essential building blocks for any practical computing platform, limiting its potential. Elasticity can address the shortcoming that today's in-network computing only supports a simple deployment model where a single application runs on a single device equipped with fixed and limited resources. Similarly, fault resiliency is critical for managing prevalent device failures for the correctness and performance of applications, but it has gained little attention. Although resource elasticity and fault resiliency have been extensively studied for traditional server-based computing, we find that enabling them on programmable networking devices is challenging, especially due to their hardware constraints and workload characteristics.

In this thesis, we argue that by designing abstractions that effectively leverage resources available outside a single type of device while hiding the complexities of dealing with device heterogeneity, we can make in-network computing more elastic and resilient without any hardware modifications. This concept, which we call device resource augmentation, is a key enabler for resource elasticity and fault resiliency for stateful in-network applications written for programmable switches. In particular, we design three systems, named TEA, ExoPlane, and RedPlane, that use this concept to provide support for elastic memory and elastic compute/ memory, and fault resiliency, respectively. Each of these systems consists of a key abstraction, programming APIs, and a runtime environment. We demonstrate their feasibility and effectiveness with prototype implementations and evaluations using various in-network applications.

### DISSERTATION ABSTRACT: Self-Driving Database Management Systems: Forecasting, Modeling, and Planning

#### Lin Ma Carnegie Mellon University, SCS

#### PhD Defense — August 18, 2021

Database management systems (DBMSs) are an important part of modern datadriven applications. However, they are notoriously difficult to deploy and administer because they have many aspects that one can change that affect their performance, including database physical design and system configuration. There are existing methods that recommend how to change these aspects of databases for an application. But most of them require humans to make final decisions on what changes to apply and when to apply them. Furthermore, these previous tuning methods either (I) require expensive exploratory testing, (2) are reactionary to the workload and can only solve problems after they occur, (3) focus only on improving one single aspect of the DBMS, or (4) do not provide explanations on their decisions. Thus, most DBMSs today still require onerous and costly human administration.

In this thesis, we present a novel architecture for a self-driving DBMS that enables automatic system management and removes the administration impediments. Our approach consists of three frameworks: (I) workload forecasting, (2) behavior modeling, and (3) action planning. The workload forecasting framework predicts the query arrival rates under varying database workload patterns using an ensemble of time-series forecasting models. The behavior modeling framework constructs fine-grained

machine learning models that predict the runtime behavior of the DBMS. Lastly, the action planning framework generates a sequence of optimization actions based on these forecasted workload patterns and behavior model estimations. It uses receding horizon control and Monte Carlo tree search to approximate the complex optimization problem effectively.

Our forecasting-modeling-planning architecture enables an autonomous DBMS that proactively plans for optimization actions without expensive testing. It automatically applies the actions at proper times, holistically controls all system aspects, and provides explanations on its decisions.

## DISSERTATION ABSTRACT: Elastic Machine Learning Systems with Co-adaptation

#### Aurick Qiao Carnegie Mellon University, SCS

PhD Defense — August 4, 2021

In recent years, the amount of computation being invested into machine learning (ML) and deep learning (DL) training has multiplied by several orders of magnitude. Under these conditions, elasticity (the ability of a system to dynamically adapt to changing supply and demand of compute resources over time) is a key ingredient for efficient resource management. Elasticity has long been proven to improve the resource utilization, execution performance, and fault tolerance of traditional applications such as web services and big data processing. However, elastic ML training is a relatively new area of interest, and faces different challenges from traditional applications due to ML training's highly sub-linear resource scalability, diverse execution patterns and strategies, and dependence between distributed workers.

This thesis steps beyond the existing early work in elastic ML by employing co-adaptation, i.e. combining both system-level and application-side adaptations, to better adapt to dynamic compute resources. Although previous frameworks can enable elasticity by relying on systemlevel implementations, they ignore the inherent resource adaptability of ML training that can be leveraged to better overcome the aforementioned challenges. We present the design, implementation, and evaluation of three elastic systems for ML that improve DL training time in shared GPU clusters by 37-50%, enable elasticity for a diverse set of ML training applications, and reduce the impact of resource failures by 78-95%.

### DISSERTATION ABSTRACT: Mitigating Memory-Safety Bugs with Efficient Out-of-Process Integrity Checking

Daming Dominic Chen Carnegie Mellon University, SCS

PhD Defense — June 17, 2021

Computer programs written in low-level languages with manual memory management, like C and C++, can contain unintentional memory safety bugs due to developer error. Examples of these bugs include spatial buffer overflows, as well as temporal use-after-frees and double frees, which can be leveraged by attackers to exploit programs by altering their runtime behavior. Indeed, statistics from both Google Chrome and Microsoft show that ~70% of all security vulnerabilities in their codebases involve memory safety bugs.

Past work has proposed various strategies to eagerly detect or lazily mitigate such bugs. Eager approaches detect memory safety bugs by checking pointer operations, whereas lazy mitigations prevent exploitation by validating program data. To improve accuracy, mitigations may need to maintain internal state (metadata) about program execution, which must also be protected from corruption. This has been achieved using different techniques, including software-based address space partitioning, and hardware-based fine-grained instruction monitoring. Nevertheless, these approaches suffer from significant complexity, brittleness, or incompatibility, which reduces their efficiency and effectiveness.

Vikramraj Sitpal, Senior Member of Technical Staff, Oracle discusses Real World Challenges in the Oracle Database Cloud at the Spring 2022 Day of Consortium Talks.

In this thesis, we observe that existing mitigations are limited by their decision to maintain internal metadata within the same process. We show that augmenting hardware with a small, secure, and efficient AppendWrite inter-process communication (IPC) primitive allows metadata storage and policy checking to be performed in a separate isolated process, which improves both security and performance. We implement this design in our HerQules framework, which we show is capable of protecting both control-flow integrity and data-flow integrity. We evaluate our approach on a variety of real-world programs, including multiple benchmark suites, the NGINX web server, and the Google Chromium web browser.

## DISSERTATION ABSTRACT: Modernizing Models and Management of the Memory Hierarchy for Non-Volatile Memory

Charles John McGuffey Carnegie Mellon University, SCS

PhD Defense — May 3, 2021

Non-volatile memory technologies (NVMs) are a new family of technologies that combine near memory level performance with near storage level cost density. The result is a new type of memory hierarchy layer that exists and performs

## **DEFENSES & PROPOSALS**

#### continued from page 13

somewhere between the two. These new technologies offer many opportunities for performance improvement, but in order to take advantage of these system design needs to account for their adapted for their particular characteristics.

In this thesis, we focus on how to design memory management and caching systems for NVMs. Our work is broken into three major categories targeting different primary performance metrics. I. We study how to design algorithms and memory management to achieve fault tolerance with low cost and efficient recovery using NVMs. 2. We design an extension the traditional model of caching to account for data writes in order to improve NVM device lifetime and energy consumption. 3. We investigate how to improve throughput in caches by taking advantage of granularity change in the memory hierarchy.

Throughout our work we rely on a blend of theoretical and practical approaches. We provide models for processor faults, cache writebacks, cache-storage communication, and trace complexity that isolate the targeted effects from orthogonal complications. For each model, we show worst case theoretical bounds for our algorithms along with proofs that explain how the benefits are derived. We then take our results and provide empirical evaluations to show their effectiveness in practice. We believe that our ideas and approach provide a solid foundational study on memory hierarchy design in the era of non-volatile memories.

## DISSERTATION ABSTRACT: Dynamic Model Specialization for Efficient Inference, Training and Supervision

Ravi Teja Mullapudi Carnegie Mellon University, SCS

PhD Defense — April 26, 2021

With the advent of deep networks a significant focus in computer vision has been on building bigger and more accurate models for a variety of tasks using large amounts of human labeled data. This large scale supervised learning approach has well known scalability challenges namely: I) accurate general models are computationally expensive for training and inference 2) collecting and labeling large datasets requires extensive human effort and 3) datasets need to be repeatedly curated due to shifts in the target distribution. However, in many contexts, the goal is to build a model for a small fraction of the general distribution of images. In this thesis, rather than trying to build general models that are accurate in a wide range of contexts, we embrace the context specific view and present techniques for rapidly building and using models specialized to a context. Specifically, we exploit temporal specialization for building efficient video segmentation models. We show that continuously specializing a compact model to the content in a video stream enables accurate and efficient inference. We leverage specialization to visually similar categories for building efficient image classification architectures. We show that by specializing model features to discriminate between visually similar categories, one can improve inference efficiency by only computing the subset of features necessary for classifying a specific image. We explore specialization to individual categories for reducing human labeling effort in building models for rare categories. We show that models specialized to individual categories reduce human effort in mining large unlabeled data collections for examples relevant to rare categories. More broadly, we demonstrate that by dynamically specializing to a moment in time, to an input scene, or to a specific object category, it is possible to train accurate models quickly, reduce

PDL Director, Greg Ganger, opens the show at the 2022 Spring Visit Day, our first in person gathering since the Fall 2019 Retreat.

inference costs, and significantly reduce the amount of supervision required for training.

#### THESIS PROPOSAL: Beyond Model Efficiency: Data Optimizations for Machine Learning Systems

Michael Kuchnik, CSD May 6, 2022

The field of machine learning has exploded due to the increased availability of data, compute, and algorithms. Systems built to support machine learning models have primarily focused on the compute path of the model itself. This thesis proposes to investigate the role of the data-path in both training and validation. For the first part of the thesis, we focus on training data, illustrating that the training data pipeline is a prime target for performance considerations. To aid in addressing performance issues, we introduce a form of training-pipeline subsampling, a reduced fidelity disk format, and a system for automatically tuning data pipeline performance knobs. In the second part, we propose to turn to the validation set of training, developing a system for automatically querying and validating a language model's behavior. We conclude with thoughts on how machine learning systems can expose data-friendly interfaces in upcoming generations of systems.

## THESIS PROPOSAL: Leveraging Emerging Storage Technologies to Improve Performance, Reliability, and Availability

Thomas Sheek Kim, CSD May 19, 2022

Zoned Namespace (ZNS) SSDs are the latest evolution of host-managed flash storage, enabling improved performance at a lower cost-per-byte than traditional block interface SSDs. However, the ZNS interface is incompatible with existing

Rekha Pitchumani, Sr. Research Manager, Samsung tells CMU personnel and industry visitors about Data-Centric Computing with Emerging Memory and Storage Devices at the Spring 2022 Day of Consortium Talks.

software, and introduces new challenges when deploying arrays of these SSDs.

This thesis builds on our existing work designing, implementing, and evaluating RAIZN, a system that exposes a logical volume with a zoned interface that provides RAID-like reliability and striping over ZNS SSDs. In this proposal, I detail our plans to implement and evaluate two major extensions to our existing system: Zone append support and configurable logical zone size.

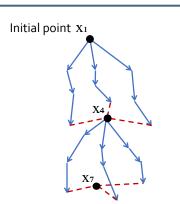

## THESIS PROPOSAL: Large-scale Machine Learning over Streaming Data

#### Ellango Jothimurugesan, CSD March 29, 2022

Training data is constantly growing over time. This thesis investigates how to continuously update machine learning models in real-time both efficiently and with high accuracy, and with a focus on the statistical challenge of adapting to changes in the data distribution over time, known as concept drift. The proposed thesis will contribute several algorithms: (i) an optimization algorithm based on variance-reduced SGD that incorporates incremental data arrivals under time-varying arrival and processing rates for IID data; (ii) an adaptive algorithm for non-IID data arrivals that extends traditional concept drift detection tests into a stable-state/ reactive-state process, attaining higher statistical accuracy and robustness to

hyperparameter selection; and (iii) a decentralized algorithm for data that is both non-IID both in time and space across nodes in a federated learning setting and allows for accurate collaborative training despite drifts. These algorithms have provable guarantees and experimentally outperform the state-of-the-art.

## THESIS PROPOSAL: Ultra-low-power, Energyminimal Computer Architectures

Graham Gobieski, CSD Dec 6, 2021

Ultra-low-power (ULP) sensor devices are increasingly being deployed for a variety of use-cases in many different environments. The applications are wide-ranging and growing in complexity, relying on sophisticated techniques like on-device machine inference and advanced digital signal processing. However, existing systems suffer fundamental inefficiencies in supplying instructions and data that demand solutions across the compute stack: from software that enables sophisticated workloads on ULP devices to new, energy-minimal computer architectures.

The objective of this work is to design a complete system stack that leverages new execution models to maximize energyefficiency without sacrificing programmability. Specifically this thesis contributes I) SONIC, a software-runtime system that enables DNN inference on intermittent, embedded devices, 2) MANIC, an ultra-low-power vectordataflow co-processor, 3) SNAFU, a energy-minimal CGRA generation framework and architecture, and 4) MANIC silicon, a silicon prototype of the MANIC co-processor. Taken together these systems form the foundation of a new stack with state-of-the-art energy efficiency, making sophisticated workloads practical, and support for programmability, allowing for iteration, development of new algorithms, and quick deployment.

Finally, to round out the new system stack, this work will discuss the ongoing characterization of the MANIC silicon prototype and the development of a new dataflow compiler to target SNAFU-like CGRAs.

### THESIS PROPOSAL: Reliable and Resource-Efficient Learning Systems via Coding-Theory-Inspired Approaches

Jack Kosaian, CSD November 10, 2021

Neural networks (NNs) are deployed in many settings, ranging from web services to safety critical systems. This has led to the development of various learning systems for deploying NNs. Learning systems must maintain high predictive performance (e.g., accuracy) while also meeting application-level objectives, such as latency constraints. However, meeting such application-level objectives is made challenging by two oftenconflicting requirements: (I) Learning systems must operate reliably despite running atop unreliable, failure-prone hardware. (2) Learning systems must use hardware efficiently.

Techniques used to improve reliability often oppose those used to improve resource efficiency. To balance these conflicting goals, many computer systems leverage coding-theoretic tools, such as error-correcting codes and erasure codes. These tools have enabled resource-efficient reliability in storage, communication, and high-performance computing systems.

This thesis explores the use of ideas inspired by coding theory to improve the reliability and resource efficiency of learning systems. We pursue this through three main thrusts:

(I) We show how properties unique to learning systems can be exploited to more-efficiently integrate traditional coding-theoretic tools into learning systems. As an example, we reduce the execution-time overhead of fault-

## **DEFENSES & PROPOSALS**

#### continued from page 15

tolerant, safety-critical NN inference on GPUs by up to 5.3x by exploiting trends in NN design and GPU hardware.

(2) We demonstrate that co-designing coding-theoretic tools with learning systems offers new opportunities to extend the reach of these tools beyond their prior limitations. Specifically, we enable resource-efficient fault tolerance in distributed prediction serving systems by using machine learning to overcome a key barrier in prior coding-theoretic tools.

(3) We identify and exploit opportunities for coding-theory-inspired ideas to be used to improve the normal-mode performance of learning systems, when reliability is not a concern. We show that the throughput and GPU utilization of specialized convolutional neural network (CNN) inference can be improved by up to 2.5x through operating over images combined in a coding-theory-inspired manner and making appropriate modifications to the CNN architecture.

This thesis demonstrates the promise of using coding-theory-inspired tools in learning systems and aims to usher adoption of these tools in learning systems, similar to how they have been used in storage and communication systems.

## THESIS PROPOSAL: On Building a Multiversioned Cache Hierarchy with Page Overlays

Ziqi Wang, CSD June 8, 2021

On modern multi-core architectures, the cache hierarchy serves as both a fast storage for frequently accessed data, and a communication channel between processor cores. Recent advancements in software and hardware, however, have motivated many interesting use cases of the cache that are not handled very well by today's cache hierarchy. This thesis proposal investigates into versioning, one of the most generally observed paradigms in daily programming but largely neglected

in cache system designs. We observe that many common problems from a wide range of applications can be addressed with hardware support for managing logically related data ("versions"). Current cache hierarchy struggles with these problems and forces software designs to adopt sub-optimal solutions, which leaves much space for improvement.

This proposal presents a systematic solution for several real-world problems that fall into the versioning category. We base our design on Page Overlays, a virtual memory framework that enables finegrained address remapping. As part of our preliminary work towards this grand goal, we present OverlayTM, a Hardware Transactional Memory (HTM) design running the multi-versioned, serializable concurrency control protocol with a hardware commit queue. We also present NVOverlay to leverage versions on different levels of the hierarchy to perform background redo logging onto NVM at millisecond-scale frequency. We next present MBC-2D as an inter-block cache compression architecture operating on the versioned "2D address space", which achieves higher compression ratio with simpler metadata management.

This proposal also seeks to extend our preliminary works in the following major directions. First, we are eager to explore malloc-less object allocation using fast incache duplication of versions without the overhead of a software allocator. Second, we propose to extend the 2D inter-block compression domain from the last-level cache to the main memory, such that blocks are also organized in 2D compressed fashion in the main memory for more logical storage and less bus bandwidth consumption. Lastly, we also plan to investigate into page table compression in a virtualized environment. This is of high value to containers and microservice platforms where the page tables, as well as the processes themselves, are short-lived.

## THESIS PROPOSAL: Compiler Techniques to Optimize Communication for Fragmented Applications

Pratik Fegade, CSD June 2, 2021

With the increasing difference between communication and computation latencies, the performance of modern application domains such as deep learning and web applications is often bottlenecked by data movement. Given the size and complexity of these applications, their individual components are often (i) designed, developed, optimized and managed independently and therefore (ii) often use a wide array of different source languages as well as other technologies. Such fragmentation of the application's logic means that compiler optimizations, traditionally shown to be highly effective at optimizing data movement, may no longer be as effective because no compiler has an end-to-end view of the entire application.

In this thesis, we develop compiler techniques to optimize communication costs by (i) explicitly breaking artificial compilation boundaries arising due to fragmentation, and (ii) specializing for the structure of the data involved. We focus on microservice-based web applications and deep learning computations that exhibit shape and control flow dynamism. Accordingly, we first discuss our work on Cortex, a compiler that performs end-to-end optimization of the control flow and tensor computations found in recursive deep learning models. We then move on to discuss a few proposed directions where we aim

to (i) develop techniques for performant handling of control flow dynamism in deep learning, (ii) expand the scope of computations handled by tensor compilers and (iii) develop automated caching techniques for microservice applications. In solving these problems, we propose solutions that cross compilation and development boundaries, allowing us to perform global optimizations to reduce communication costs.

## THESIS PROPOSAL: A Principled Approach to Parallel Job Scheduling

#### Benjamin Berg, CSD May 10, 2021

Parallelizable workloads are ubiquitous and appear across a diverse array of modern computer systems. Data centers, supercomputers, machine learning clusters, distributed computing frameworks, and databases all process jobs designed to be parallelized across many servers or cores. A job will receive some speedup from being parallelized across additional servers or cores, allowing the job to complete more quickly. However, jobs generally cannot be perfectly parallelized, and receive diminishing returns from being allocated additional servers. Hence, given a fixed number of servers, it is not obvious how to allocate servers across a set of jobs in order to reduce the response times of the jobs - the times from when each job arrives to the system until it is completed. While this question has been considered by the worstcase scheduling community, existing results are hampered by strong lower bounds on worst-case performance and tend to suggest policies which do not work well in practice. The goal of this thesis is to develop and analyze practical policies for scheduling parallelizable jobs using the tools of performance modeling and stochastic analysis.

Our approach in developing new scheduling policies for parallelizable jobs is threefold. First, we develop new stochastic models of parallelizable jobs running in a multi-server system. Second, we analyze these new models using the tools of stochastic performance modeling, showing that a stochastic analysis emits scheduling policies which outperform the policies suggested by the worst-case literature. Finally, we validate our theoretical models through both simulation and real-world implementation to show that the scheduling policies we derive work well in practice. We apply this methodology to a variety of practical settings where systems are required to schedule parallelizable jobs. We consider the case where job sizes are completely unknown to the system, the case where job sizes are perfectly known to the system, and the case where job sizes are known to follow general distributions. Similarly, we consider the case where jobs are all assumed to have the same scaling behavior, the case where some jobs are more parallelizable than others, and the case where a job's parallelizability can change over time.

## **RECENT PUBLICATIONS**

#### continued from page 7

Experiments show that RAIZN provides full expected performance from the aggregate device set, successfully addressing the key challenges from the ZNS interface. RAIZN achieves throughput and latency comparable to the equivalent Linux software RAID implementation running on conventional SSDs that use the same hardware platform, and then RAIZN exceeds its performance once device-level garbage collection inhibits the conventional SSDs. Importantly, RAIZN retains ZNS's opportunities for increased application performance, allowing higher-level software (e.g., F2FS or RocksDB) to carefully control garbage collection. This allows, for example, RAIZN to maintain consistent performance under scenarios where conventional SSD arrays experience up to 87.5% throughput drop due to device-level garbage collection.

### Are You Sure You Want to Use MMAP in Your Database Management System?

Andrew Crotty, Viktor Leis, Andrew Pavlo

12th Annual Conference on Innovative Data Systems Research (CIDR '22). January 9-12, 2022, Chaminade, USA.

Memory-mapped (mmap) file I/O is an OS-provided feature that maps the contents of a file on secondary storage into a program's address space. The program then accesses pages via pointers as if the file resided entirely in memory. The OS transparently loads pages only when the program references them and automatically evicts pages if memory fills up. mmap's perceived ease of use has seduced database management system (DBMS) developers for decades as a viable alternative to implementing a buffer pool. There are, however, severe correctness and performance issues with mmap that are not immediately apparent. Such problems make it difficult, if not impossible, to use mmap correctly and efficiently in a modern DBMS. In fact, several popular DBMSs initially used mmap to support larger-than-memory databases but soon encountered these hidden perils, forcing them to switch to managing file I/O themselves after significant engineering costs. In this way, mmap and DBMSs are like coffee and spicy food: an unfortunate combination that becomes obvious after the fact.

Since developers keep trying to use mmap in new DBMSs, we wrote this paper to provide a warning to others

#### continued from page 17

that mmap is not a suitable replacement for a traditional buffer pool. We discuss the main shortcomings of mmap in detail, and our experimental analysis demonstrates clear performance limitations. Based on these findings, we conclude with a prescription for when DBMS developers might consider using mmap for file I/O.

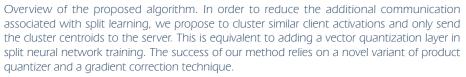

## FedLite: A Scalable Approach for Federated Learning on Resource-constrained Clients

Jianyu Wang, Hang Qi, Ankit Singh Rawat, Sashank Reddi, Sagar Waghmare, Felix X. Yu, Gauri Joshi

arXiv:2201.11865v2 [cs.LG] 16 February 2022.